- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄383875 > T7234 Compliance with the New ETSI PSD Requirement PDF資料下載

參數(shù)資料

| 型號(hào): | T7234 |

| 英文描述: | Compliance with the New ETSI PSD Requirement |

| 中文描述: | 符合新的ETSI PSD的要求 |

| 文件頁(yè)數(shù): | 31/116頁(yè) |

| 文件大小: | 1056K |

| 代理商: | T7234 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)當(dāng)前第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)第69頁(yè)第70頁(yè)第71頁(yè)第72頁(yè)第73頁(yè)第74頁(yè)第75頁(yè)第76頁(yè)第77頁(yè)第78頁(yè)第79頁(yè)第80頁(yè)第81頁(yè)第82頁(yè)第83頁(yè)第84頁(yè)第85頁(yè)第86頁(yè)第87頁(yè)第88頁(yè)第89頁(yè)第90頁(yè)第91頁(yè)第92頁(yè)第93頁(yè)第94頁(yè)第95頁(yè)第96頁(yè)第97頁(yè)第98頁(yè)第99頁(yè)第100頁(yè)第101頁(yè)第102頁(yè)第103頁(yè)第104頁(yè)第105頁(yè)第106頁(yè)第107頁(yè)第108頁(yè)第109頁(yè)第110頁(yè)第111頁(yè)第112頁(yè)第113頁(yè)第114頁(yè)第115頁(yè)第116頁(yè)

Data Sheet

January 1998

T7256 Single-Chip NT1 (SCNT1) Transceiver

Lucent Technologies Inc.

27

Microprocessor Interface Description

(continued)

Registers

(continued)

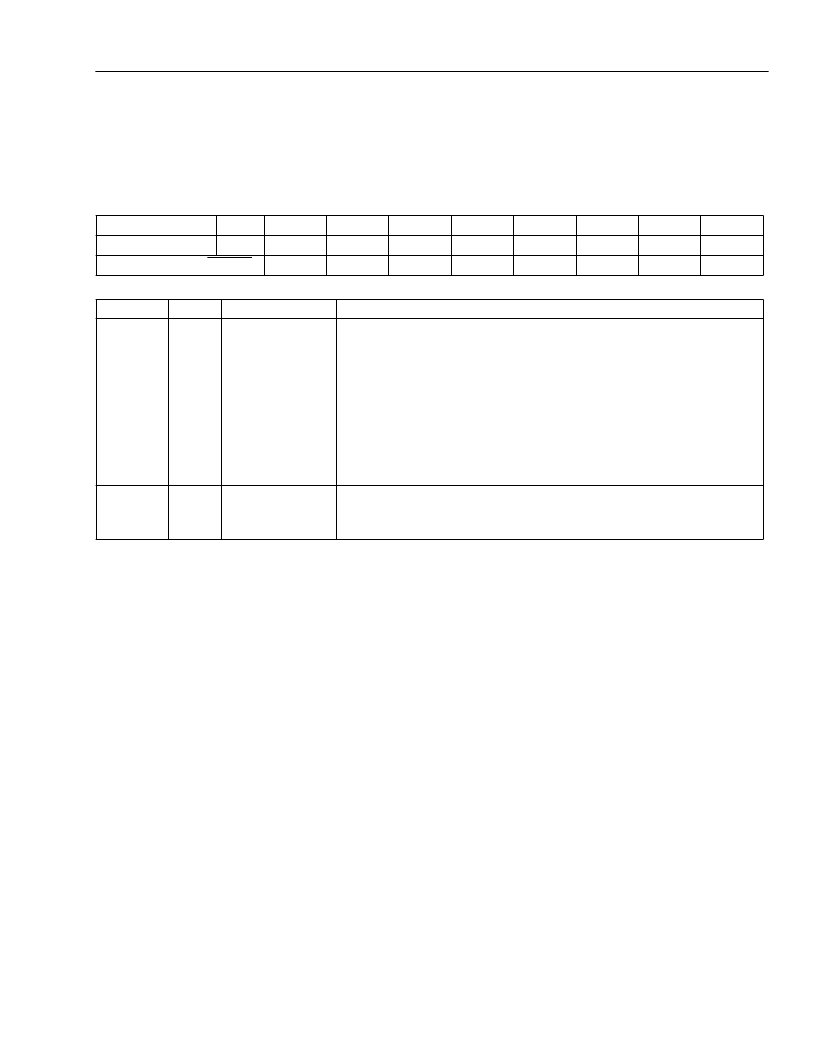

Table 9. TDM Bus Timing Control (Address 05h)

Bits 0—4 are enabled only if TDMEN = 0 (register GR2, bit 5) and one or more of bits DFR1[2:7] are set to 0.

Reg

TDR0

R/W

R/W

Bit 7

—

—

Bit 6

—

—

Bit 5

—

—

Bit 4

—

—

Bit 3

FSP

1

Bit 2

FSC2

1

Bit 1

FSC1

1

Bit 0

FSC0

1

Default State on RESET

Register

TDR0

Bit

2—0

Symbol

FSC[2:0]

Name/Description

Frame Strobe (FS) Control.

Selects location of strobe envelope within

TDM bus time slots.

000—S/T-interface 2B+D channel strobe (18-bit envelope).

001—U-interface 2B+D channel strobe (18-bit envelope).

010—S/T-interface B2 channel strobe (8-bit envelope).

011—U-interface B2 channel strobe (8-bit envelope).

100—S/T-interface D channel strobe (2-bit envelope).

101—U-interface D channel strobe (2-bit envelope).

110—S/T-interface B1 channel strobe (8-bit envelope).

111—U-interface B1 channel strobe (8-bit envelope) (default).

Frame Strobe (FS) Polarity.

0—Active-low envelope.

1—Active-high envelope (default).

TDR0

3

FSP

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| T7234A | Compliance with the New ETSI PSD Requirement |

| T7237A | Compliance with the New ETSI PSD Requirement |

| T7256A | Compliance with the New ETSI PSD Requirement |

| T7288 | CEPT/E1 Line Interface(CEPT/E1 線接口) |

| T7290A | DS1/T1/CEPT/E1 Line Interface(DS1/T1/CEPT/E1 線接口) |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| T7234A | 制造商:AGERE 制造商全稱:AGERE 功能描述:Compliance with the New ETSI PSD Requirement |

| T7237 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Compliance with the New ETSI PSD Requirement |

| T7237A | 制造商:AGERE 制造商全稱:AGERE 功能描述:Compliance with the New ETSI PSD Requirement |

| T7240 | 制造商:TE Connectivity 功能描述: |

| T7-241A5 | 功能描述:撥動(dòng)開(kāi)關(guān) ON NONE OFF 2 Pole Standard Bat Handle RoHS:否 制造商:OTTO 觸點(diǎn)形式: 開(kāi)關(guān)功能: 電流額定值: 電壓額定值 AC: 電壓額定值 DC: 功率額定值: 端接類型: 安裝風(fēng)格: 端子密封: 觸點(diǎn)電鍍: 照明: |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。