- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄383875 > T7234 Compliance with the New ETSI PSD Requirement PDF資料下載

參數(shù)資料

| 型號(hào): | T7234 |

| 英文描述: | Compliance with the New ETSI PSD Requirement |

| 中文描述: | 符合新的ETSI PSD的要求 |

| 文件頁(yè)數(shù): | 21/116頁(yè) |

| 文件大小: | 1056K |

| 代理商: | T7234 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)當(dāng)前第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)第69頁(yè)第70頁(yè)第71頁(yè)第72頁(yè)第73頁(yè)第74頁(yè)第75頁(yè)第76頁(yè)第77頁(yè)第78頁(yè)第79頁(yè)第80頁(yè)第81頁(yè)第82頁(yè)第83頁(yè)第84頁(yè)第85頁(yè)第86頁(yè)第87頁(yè)第88頁(yè)第89頁(yè)第90頁(yè)第91頁(yè)第92頁(yè)第93頁(yè)第94頁(yè)第95頁(yè)第96頁(yè)第97頁(yè)第98頁(yè)第99頁(yè)第100頁(yè)第101頁(yè)第102頁(yè)第103頁(yè)第104頁(yè)第105頁(yè)第106頁(yè)第107頁(yè)第108頁(yè)第109頁(yè)第110頁(yè)第111頁(yè)第112頁(yè)第113頁(yè)第114頁(yè)第115頁(yè)第116頁(yè)

Data Sheet

January 1998

T7256 Single-Chip NT1 (SCNT1) Transceiver

Lucent Technologies Inc.

17

U-Interface Description

At the U-interface, the T7256 conforms to ANSI T1.601

and ETSI ETR 080 when used with the proper line

interface circuitry. The T7256 Reference Circuit

description in the Application Briefs section of this doc-

ument describes a detailed example of a U-interface

circuit design.

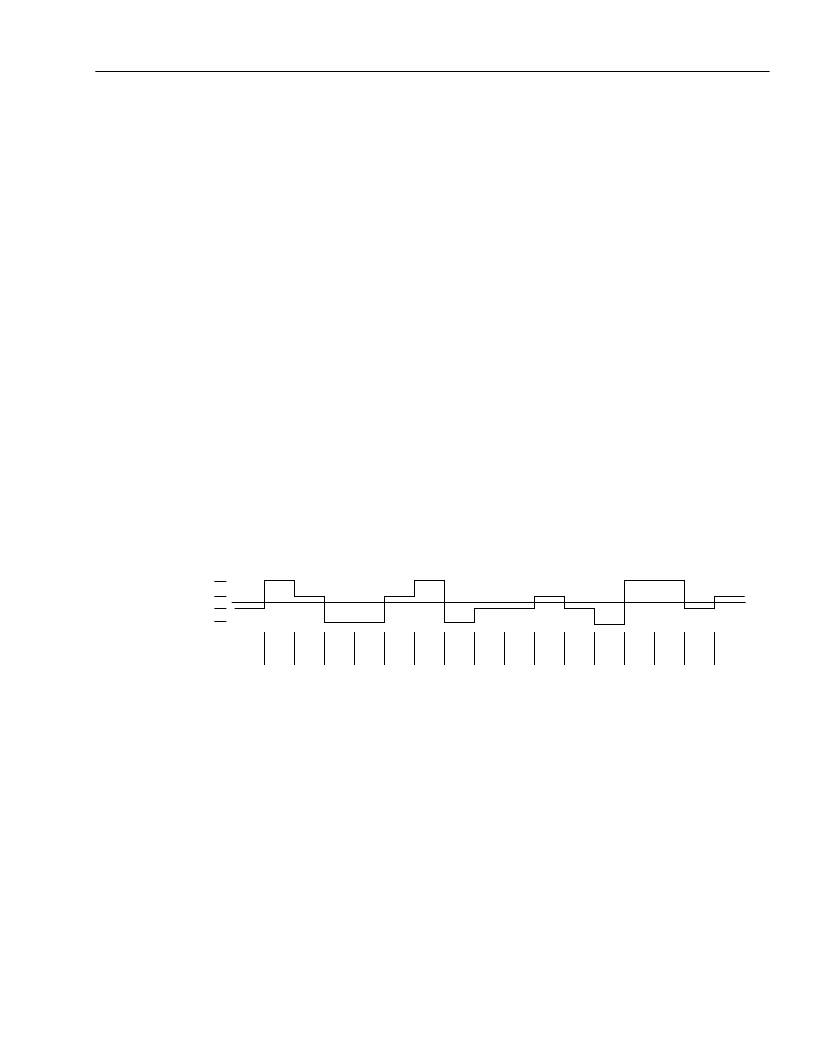

The 2B1Q line code provides a four-level (quaternary)

pulse amplitude modulation code with no redundancy.

Data is grouped into pairs of bits for conversion to qua-

ternary (quat) symbols. Figure 9 shows an example of

this coding method.

The U-interface transceiver section provides the 2B1Q

line coder (D/A conversion), pulse shaper, line driver,

first-order line balance network, clock regeneration,

and sigma-delta A/D conversion. The line driver, when

connected to the proper transformer and interface cir-

cuitry, generates pulses which meet the required 2B1Q

templates. The A/D converter is implemented by using

a double-loop, sigma-delta modulator.

The U transceiver block also takes input from the data

flow matrix and formats this information for the U-inter-

face (see Figure 1). During this formatting, synchroni-

zation bits for U framing are added and a scrambling

algorithm is applied. This data is then transferred to the

2B1Q encoder for transmission over the U-interface.

Signals received from the U-interface are first passed

through the sigma-delta A/D converter, and then sent

to the digital signal processor for more extensive signal

processing. The block provides decimation of the

sigma-delta output, linear and nonlinear echo cancella-

tion, automatic gain control, signal detection, phase

shift interpolation, decision feedback equalization, tim-

ing recovery, descrambling, and line-code polarity

detection. The decision feedback equalizer circuit pro-

vides the functionality necessary for proper operation

on subscriber loops with bridged taps.

A crystal oscillator provides the 15.36 MHz master

clock for the device. The on-chip, phase-locked loop

provides the ability to synchronize the chip to the line

rate.

The U-interface provides rapid cold start and warm

start operation. From a cold start, the device is typically

operational within four seconds. The interface supports

activation/deactivation, and when properly deactivated,

it stores the adaptive filter coefficients permitting a

warm start on the next activation request. A warm start

typically requires 200 ms for the device to become

operational.

5-2294 (C)

Figure 9. U-Interface Quat Example

–1

01

+3

10

+1

11

–3

00

–3

00

+1

11

+3

10

–3

00

–1

01

–1

01

+1

11

–1

01

–3

00

+3

10

+3

10

–1

01

+1

11

+3

+1

–1

–3

QUAT SYMBOL

BIT CODING

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| T7234A | Compliance with the New ETSI PSD Requirement |

| T7237A | Compliance with the New ETSI PSD Requirement |

| T7256A | Compliance with the New ETSI PSD Requirement |

| T7288 | CEPT/E1 Line Interface(CEPT/E1 線接口) |

| T7290A | DS1/T1/CEPT/E1 Line Interface(DS1/T1/CEPT/E1 線接口) |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| T7234A | 制造商:AGERE 制造商全稱:AGERE 功能描述:Compliance with the New ETSI PSD Requirement |

| T7237 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Compliance with the New ETSI PSD Requirement |

| T7237A | 制造商:AGERE 制造商全稱:AGERE 功能描述:Compliance with the New ETSI PSD Requirement |

| T7240 | 制造商:TE Connectivity 功能描述: |

| T7-241A5 | 功能描述:撥動(dòng)開關(guān) ON NONE OFF 2 Pole Standard Bat Handle RoHS:否 制造商:OTTO 觸點(diǎn)形式: 開關(guān)功能: 電流額定值: 電壓額定值 AC: 電壓額定值 DC: 功率額定值: 端接類型: 安裝風(fēng)格: 端子密封: 觸點(diǎn)電鍍: 照明: |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。