- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄384024 > TMX320DM6446ZWT (Texas Instruments, Inc.) Digital Media System on-Chip PDF資料下載

參數(shù)資料

| 型號: | TMX320DM6446ZWT |

| 廠商: | Texas Instruments, Inc. |

| 英文描述: | Digital Media System on-Chip |

| 中文描述: | 數(shù)字媒體系統(tǒng)芯片 |

| 文件頁數(shù): | 64/214頁 |

| 文件大?。?/td> | 1699K |

| 代理商: | TMX320DM6446ZWT |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁當前第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁第107頁第108頁第109頁第110頁第111頁第112頁第113頁第114頁第115頁第116頁第117頁第118頁第119頁第120頁第121頁第122頁第123頁第124頁第125頁第126頁第127頁第128頁第129頁第130頁第131頁第132頁第133頁第134頁第135頁第136頁第137頁第138頁第139頁第140頁第141頁第142頁第143頁第144頁第145頁第146頁第147頁第148頁第149頁第150頁第151頁第152頁第153頁第154頁第155頁第156頁第157頁第158頁第159頁第160頁第161頁第162頁第163頁第164頁第165頁第166頁第167頁第168頁第169頁第170頁第171頁第172頁第173頁第174頁第175頁第176頁第177頁第178頁第179頁第180頁第181頁第182頁第183頁第184頁第185頁第186頁第187頁第188頁第189頁第190頁第191頁第192頁第193頁第194頁第195頁第196頁第197頁第198頁第199頁第200頁第201頁第202頁第203頁第204頁第205頁第206頁第207頁第208頁第209頁第210頁第211頁第212頁第213頁第214頁

www.ti.com

P

3.5

Configurations at Reset

3.5.1

Device Configuration at Device Reset

3.5.2

Peripheral Selection at Device Reset

TMS320DM6446

Digital Media System on-Chip

SPRS283–DECEMBER 2005

3.4.3.1

Host-Boot Mode

In host boot mode, the ARM is the master and controls the reset and boot of the C64x+. The C64x+ DSP

remains powered-off after device reset. The ARM is responsible for enabling power to the C64x+ and

releasing it from reset (PSC MMR bits: MDCTL[39].LRST and MRSTOUT1.MRSTz[39]). Prior to releasing

the C64x+ reset, the ARM must program the address from which the C64x+ will begin execution in the

DSPBOOTADDR register.

3.4.3.2

Self-Boot Mode

In self-boot mode, the C64x+ power domain is turned on and the C64x+ DSP is released from reset

without ARM intervention. The C64x+ begins execution from the default EMIFA address (0x4220 0000)

contained within the DSPBOOTADDR register. The C64x+ begins execution with instruction (L1P) cache

enabled.

The following sections give information on configuration settings for the device at reset.

Table 3-11

shows a summary of device inputs required for booting the ARM and DSP, and configuring

EMIFA data and address bus widths for proper operation of the device at the rising edge of the RESET

input.

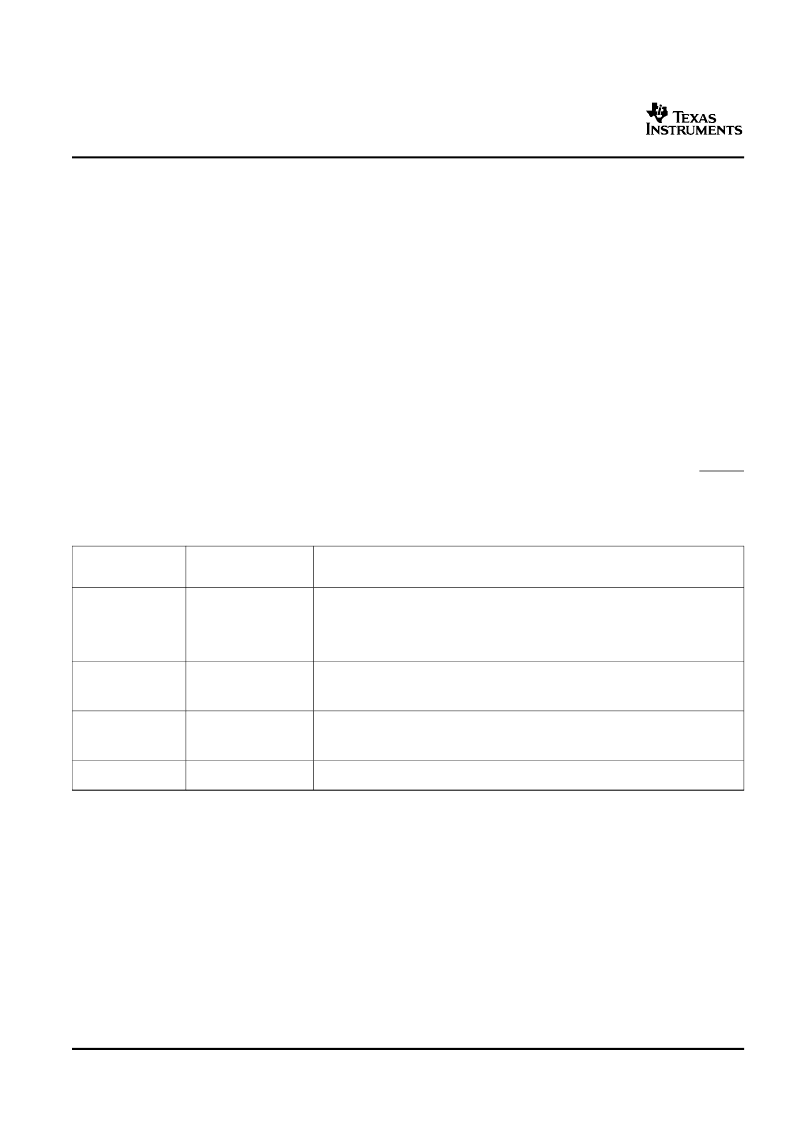

Table 3-11. Device Configurations (Input Pins Sampled at Reset)

DEVICE SIGNALS

SAMPLED

AT RESET

BTSEL[1:0]

DEVICE SIGNAL NAME

AFTER RESET

DESCRIPTION

COUT[1:0]

ARM Boot mode selection pins.

‘00’ indicates ARM boots from ROM (NAND Flash).

‘01’ indicates that ARM boots from EMIFA (NOR Flash).

‘10’ Reserved.

‘11’ indicates that ARM boots from ROM (UART).

DSP Boot mode selection pin.

DSP_BT

COUT3

‘0’ sets ARM boot of C64x+.

‘1’ sets C64x+ self boot.

EMIFA data bus width selection pin.

EM_WIDTH

COUT2

‘0’ sets EMIFA to 8-bit data bus width

‘1’ sets EMIFA to 16-bit data bus width.

EMIFA address bus width selection pins for EMIFA address pins multiplexed with GPIO.

See

Table 3-12

,

Table 3-13

, and

Table 3-14

for details.

AEAW[4:0]

YOUT[4:0]

As briefly mentioned in

Table 3-11

, the state of the AEAW[4:0] pins captured at reset configures the

number of EMIFA address pins required for device boot. These values are stored in the AEAW field of the

PINMUX0 register. At reset, this provides proper addressing for external boot. Unused address pins are

available for use as GPIO. The register settings are software programmable after reset.

Table 3-12

,

Table 3-13

, and

Table 3-14

show the AEAW[4:0] bit settings and the corresponding multiplexing for

EMIFA address and GPIO pins.

The number of EMIFA address bits enabled is configurable from 0 to 23. EM_BA[1] and EM_A[21:0] pins

that are not assigned to another peripheral and not enabled as address signals become GPIO pins. The

enabled address pins are always contiguous from EM_BA[1] upwards and address bits cannot be skipped.

64

Device Configuration

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| TN28F010-90 | 28F010 1024K (128K X 8) CMOS FLASH MEMORY |

| TN28F010-120 | 28F010 1024K (128K X 8) CMOS FLASH MEMORY |

| TN28F010-150 | 28F010 1024K (128K X 8) CMOS FLASH MEMORY |

| TN28F020-90 | 28F020 2048K (256K X 8) CMOS FLASH MEMORY |

| TN28F020-150 | 28F020 2048K (256K X 8) CMOS FLASH MEMORY |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| TMX320DM6467TZUT1 | 制造商:Texas Instruments 功能描述: |

| TMX320DM6467ZUT | 功能描述:數(shù)字信號處理器和控制器 - DSP, DSC Dig Media System-on- Chip RoHS:否 制造商:Microchip Technology 核心:dsPIC 數(shù)據(jù)總線寬度:16 bit 程序存儲器大小:16 KB 數(shù)據(jù) RAM 大小:2 KB 最大時鐘頻率:40 MHz 可編程輸入/輸出端數(shù)量:35 定時器數(shù)量:3 設(shè)備每秒兆指令數(shù):50 MIPs 工作電源電壓:3.3 V 最大工作溫度:+ 85 C 封裝 / 箱體:TQFP-44 安裝風格:SMD/SMT |

| TMX320DM647ZUT720 | 制造商:TI 制造商全稱:Texas Instruments 功能描述:Digital Media Processor |

| TMX320DM647ZUT900 | 制造商:TI 制造商全稱:Texas Instruments 功能描述:Digital Media Processor |

| TMX320DM648ACUT7 | 制造商:Texas Instruments 功能描述:- Trays |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。