- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄384024 > TMX320DM6446ZWT (Texas Instruments, Inc.) Digital Media System on-Chip PDF資料下載

參數(shù)資料

| 型號: | TMX320DM6446ZWT |

| 廠商: | Texas Instruments, Inc. |

| 英文描述: | Digital Media System on-Chip |

| 中文描述: | 數(shù)字媒體系統(tǒng)芯片 |

| 文件頁數(shù): | 151/214頁 |

| 文件大小: | 1699K |

| 代理商: | TMX320DM6446ZWT |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁第107頁第108頁第109頁第110頁第111頁第112頁第113頁第114頁第115頁第116頁第117頁第118頁第119頁第120頁第121頁第122頁第123頁第124頁第125頁第126頁第127頁第128頁第129頁第130頁第131頁第132頁第133頁第134頁第135頁第136頁第137頁第138頁第139頁第140頁第141頁第142頁第143頁第144頁第145頁第146頁第147頁第148頁第149頁第150頁當前第151頁第152頁第153頁第154頁第155頁第156頁第157頁第158頁第159頁第160頁第161頁第162頁第163頁第164頁第165頁第166頁第167頁第168頁第169頁第170頁第171頁第172頁第173頁第174頁第175頁第176頁第177頁第178頁第179頁第180頁第181頁第182頁第183頁第184頁第185頁第186頁第187頁第188頁第189頁第190頁第191頁第192頁第193頁第194頁第195頁第196頁第197頁第198頁第199頁第200頁第201頁第202頁第203頁第204頁第205頁第206頁第207頁第208頁第209頁第210頁第211頁第212頁第213頁第214頁

www.ti.com

P

Start

D0

D1

Dx

End

7

SD_CLK

SD_DATx

9

10

4

3

3

4

5.13

Video Processing Sub-System (VPSS) Overview

5.13.1

Video Processing Front-End (VPFE)

TMS320DM6446

Digital Media System on-Chip

SPRS283–DECEMBER 2005

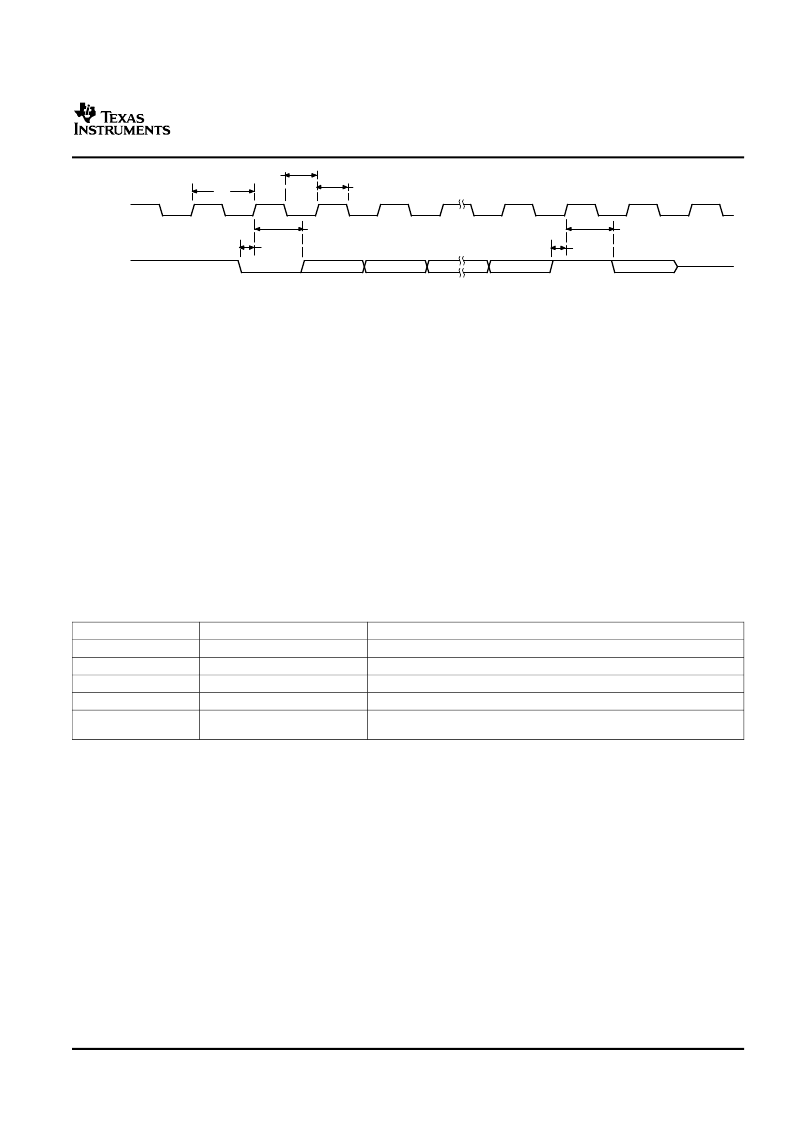

Figure 5-40. MMC/SD Host Read and Card CRC Status Timing

The DM6446 Video Processing Sub-System (VPSS) provides a Video Processing Front End (VPFE) input

interface for external imaging peripherals (i.e., image sensors, video decoders, etc.) and a Video

Processing Back End (VPBE) output interface for display devices, such as analog SDTV displays, digital

LCD panels, HDTV video encoders, etc.

Note:

The VPSS module is supported with Linux Application Peripheral Interfaces (APIs) commonly used

by video application developers. Video for Linux 2 or V4L2 uses APIs commonly used for video capture.

The typical use cases of the VPSS Video Front-End (VPFE) have been ported to this Linux API structure.

V4L2 supports standard video interfaces such as: BT.656 and Y/C mode. Other modules within the VPSS

VPFE for example, the Preview Engine, H3A, and Histogram are

not

currently supported within the

software APIs. The VPSS Back-End (VPBE) uses FBDev/DirectFB as the APIs. Certain functionalities

within the VPBE have not been implemented in the FBDev/DirectFB APIs. For modes/functions not

implemented in software, it is user's responsibility to modify the software drivers/APIs.

The VPSS register memory mapping is shown in

Table 5-41

.

Table 5-41. VPSS Register Descriptions

HEX ADDRESS RANGE

0x01C7 3400

0x01C7 3404

0x01C7 3408

0x01C7 3508

0x01C7 350C -

0x01C7 3FFF

REGISTER ACRONYM

Description

PID

PCR

-

SDR_REG_EXP

-

Peripheral Revision and Class Information

VPSS Control Register

Reserved

SDRAM Non Real-Time Read Request Expand

Reserved

The Video Processing Front-End (VPFE) consists of the CCD Controller (CCDC), Preview Engine,

Resizer, Hardware 3A (H3A) Statistic Generator, and Histogram blocks. Together, these modules provide

DM6446 with a powerful and flexible front-end interface. These modules are briefly described below:

The CCDC provides an interface to image sensors and digital video sources.

The Preview Engine is a parameterized hardwired image processing block which is used for converting

RAW color data from a Bayer pattern to YUV4:2:2.

The Resizer module re-sizes the input image data to the desired display or video encoding resolution

The H3A module provides control loops for Auto Focus (AF), Auto White Balance (AWB) and Auto

Exposure (AE).

The Histogram module bins input color pixels, depending on the amplitude, and provides statistics

required to implement various 3A (AE/AF/AWB) algorithms and tune the final image/video output.

The VPFE register memory mapping is shown in

Table 5-42

.

Peripheral and Electrical Specifications

151

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| TN28F010-90 | 28F010 1024K (128K X 8) CMOS FLASH MEMORY |

| TN28F010-120 | 28F010 1024K (128K X 8) CMOS FLASH MEMORY |

| TN28F010-150 | 28F010 1024K (128K X 8) CMOS FLASH MEMORY |

| TN28F020-90 | 28F020 2048K (256K X 8) CMOS FLASH MEMORY |

| TN28F020-150 | 28F020 2048K (256K X 8) CMOS FLASH MEMORY |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| TMX320DM6467TZUT1 | 制造商:Texas Instruments 功能描述: |

| TMX320DM6467ZUT | 功能描述:數(shù)字信號處理器和控制器 - DSP, DSC Dig Media System-on- Chip RoHS:否 制造商:Microchip Technology 核心:dsPIC 數(shù)據(jù)總線寬度:16 bit 程序存儲器大小:16 KB 數(shù)據(jù) RAM 大小:2 KB 最大時鐘頻率:40 MHz 可編程輸入/輸出端數(shù)量:35 定時器數(shù)量:3 設(shè)備每秒兆指令數(shù):50 MIPs 工作電源電壓:3.3 V 最大工作溫度:+ 85 C 封裝 / 箱體:TQFP-44 安裝風格:SMD/SMT |

| TMX320DM647ZUT720 | 制造商:TI 制造商全稱:Texas Instruments 功能描述:Digital Media Processor |

| TMX320DM647ZUT900 | 制造商:TI 制造商全稱:Texas Instruments 功能描述:Digital Media Processor |

| TMX320DM648ACUT7 | 制造商:Texas Instruments 功能描述:- Trays |

發(fā)布緊急采購,3分鐘左右您將得到回復。