- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄383967 > TSB82AA2I (Texas Instruments, Inc.) 1394b OHCI-LYNX CONTROLLER PDF資料下載

參數(shù)資料

| 型號: | TSB82AA2I |

| 廠商: | Texas Instruments, Inc. |

| 英文描述: | 1394b OHCI-LYNX CONTROLLER |

| 中文描述: | 的1394b OHCI的山貓控制器 |

| 文件頁數(shù): | 61/104頁 |

| 文件大小: | 461K |

| 代理商: | TSB82AA2I |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁當(dāng)前第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁

419

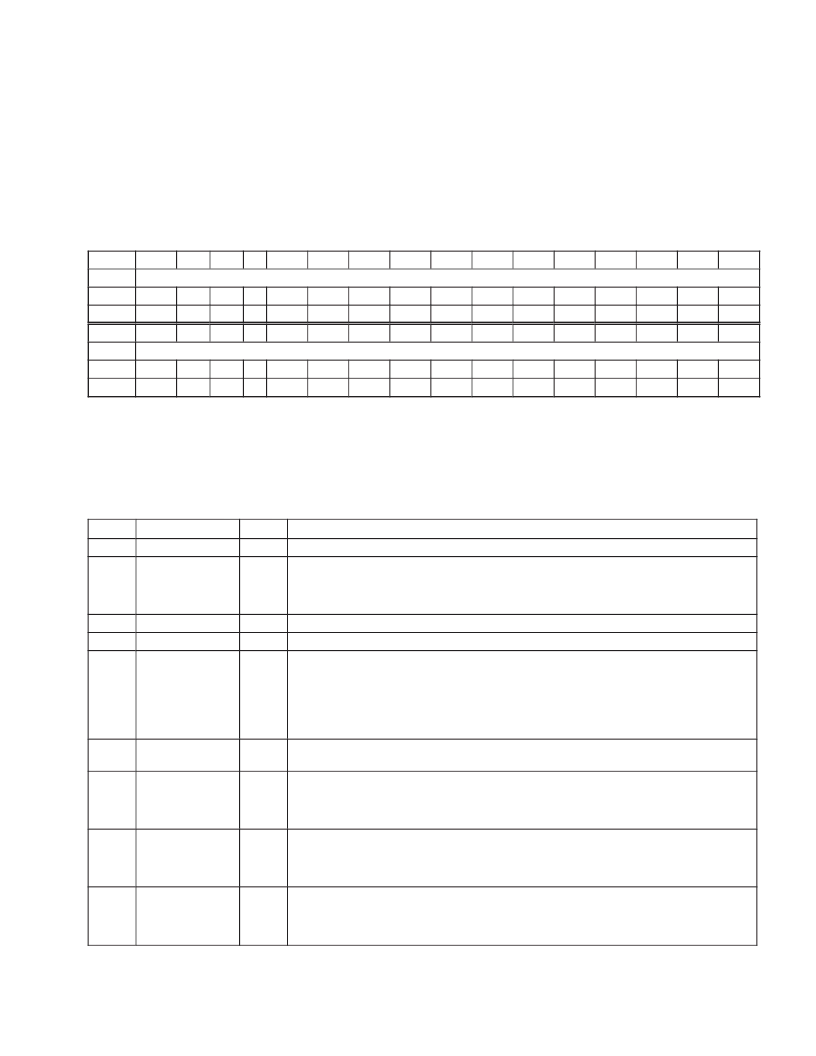

4.21 Interrupt Event Register

The interrupt event set/clear register reflects the state of the various TSB82AA2 interrupt sources. The interrupt bits

are set to 1 by an asserting edge of the corresponding interrupt signal or by writing a 1 in the corresponding bit in the

set register. The only mechanism to clear a bit in this register is to write a 1 to the corresponding bit in the clear register.

This register is fully compliant with

1394 Open Host Controller Interface Specification

, and the TSB82AA2 device

adds a vendor-specific interrupt function to bit 30. When the interrupt event register is read, the return value is the

bit-wise AND function of the interrupt event and interrupt mask registers. See Table 416 for a complete description

of the register contents.

Bit

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

16

Name

Interrupt event

Type

R

RSC

RSC

R

RSCU

RSCU

RSCU

RSCU

RSCU

RSCU

RSCU

RSCU

RSCU

RSCU

RSCU

RSCU

Default

0

X

0

0

0

X

X

X

X

X

X

X

X

0

X

X

Bit

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

Name

Interrupt event

Type

RSCU

R

R

R

R

R

RSCU

RSCU

RU

RU

RSCU

RSCU

RSCU

RSCU

RSCU

RSCU

Default

0

0

0

Interrupt event

Read/Set/Clear/Update, Read/Set/Clear, Read/Update, Read-only

80h

set register

84h

clear register [returns the content of the interrupt event register bit-wise ANDed with

the interrupt mask register when read]

XXXX 0XXXh

Table 416. Interrupt Event Register Description

0

0

0

X

X

X

X

X

X

X

X

X

X

Register:

Type:

Offset:

Default:

BIT

FIELD NAME

TYPE

DESCRIPTION

31

RSVD

R

Reserved. Bit 31 returns 0 when read.

30

vendorSpecific

RSC

This vendor-specific interrupt event is reported when either of the general-purpose interrupts are

asserted. The general-purpose interrupts are enabled by setting the corresponding bits INT_3EN

and INT_2EN (bits 31 and 23, respectively) to 1 in the GPIO control register at offset FCh in the PCI

configuration space (see Section 3.26,

GPIO Control Register

).

29

SoftInterrupt

RSC

Software interrupt. Bit 29 is used by software to generate a TSB82AA2 interrupt for its own use.

28

RSVD

R

Reserved. Bit 28 returns 0 when read.

27

ack_Tardy

RSCU

Bit 27 is set to 1 when bit 29 (ack_Tardy_enable) in the host controller control register at OHCI offset

50h/54h (see Section 4.16,

Host Controller Control Register

) is set to 1 and any of the following

conditions occur:

a. Data is present in the receive FIFO that is to be delivered to the host.

b. The physical response unit is busy processing requests or sending responses.

c. The TSB82AA2 device sent an ack_tardy acknowledgement.

26

phyRegRcvd

RSCU

The TSB82AA2 device has received a PHY register data byte which can be read from bits 2316 in

the PHY layer control register at OHCI offset ECh (see Section 4.33,

PHY Layer Control Register

).

25

cycleTooLong

RSCU

If bit 21 (cycleMaster) in the link control register at OHCI offset E0h/E4h (see Section 4.31,

Link

Control Register

) is set to 1, then this indicates that over 125

μ

s have elapsed between the start of

sending a cycle start packet and the end of a subaction gap. Bit 21 (cycleMaster) in the link control

register is cleared by this event.

24

unrecoverableError

RSCU

This event occurs when the TSB82AA2 device encounters any error that forces it to stop operations

on any or all of its subunits, for example, when a DMA context sets its dead bit to 1. While bit 24 is

set to 1, all normal interrupts for the context(s) that caused this interrupt are blocked from being set

to 1.

23

cycleInconsistent

RSCU

A cycle start was received that had values for cycleSeconds and cycleCount fields that are different

from the values in bits 3125 (cycleSeconds field) and bits 2412 (cycleCount field) in the

isochronous cycle timer register at OHCI offset F0h (see Section 4.34,

Isochronous Cycle Timer

Register

).

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| TSC2200EVM | TSC2200 Touch Screen Controller Evaluation Module(TSC2200觸摸屏控制器評估模塊) |

| TSC427CBA | Dual Power MOSFET Drivers |

| TSC427CPA | Dual Power MOSFET Drivers |

| TSC428CBA | Dual Power MOSFET Drivers |

| TSC426CBA | Dual Power MOSFET Drivers |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| TSB82AA2IPGE | 功能描述:接口 - 專用 OHCI-Lynx Controller RoHS:否 制造商:Texas Instruments 產(chǎn)品類型:1080p60 Image Sensor Receiver 工作電源電壓:1.8 V 電源電流:89 mA 最大功率耗散: 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:BGA-59 |

| TSB82AA2IPGEEP | 功能描述:1394 接口集成電路 Mil Enh 1394b OHCI- Lynx Cntrlr RoHS:否 制造商:Texas Instruments 類型:Link Layer Controller 工作電源電壓: 封裝 / 箱體:LQFP 封裝:Tray |

| TSB82AA2PGE | 功能描述:1394 接口集成電路 OHCI-Lynx Controller RoHS:否 制造商:Texas Instruments 類型:Link Layer Controller 工作電源電壓: 封裝 / 箱體:LQFP 封裝:Tray |

| TSB82AA2PGEG4 | 功能描述:1394 接口集成電路 OHCI-Lynx Controller RoHS:否 制造商:Texas Instruments 類型:Link Layer Controller 工作電源電壓: 封裝 / 箱體:LQFP 封裝:Tray |

| TSB82AA2ZGW | 功能描述:1394 接口集成電路 OHCI-Lynx Controller RoHS:否 制造商:Texas Instruments 類型:Link Layer Controller 工作電源電壓: 封裝 / 箱體:LQFP 封裝:Tray |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。