- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄383967 > TSB82AA2I (Texas Instruments, Inc.) 1394b OHCI-LYNX CONTROLLER PDF資料下載

參數(shù)資料

| 型號(hào): | TSB82AA2I |

| 廠商: | Texas Instruments, Inc. |

| 英文描述: | 1394b OHCI-LYNX CONTROLLER |

| 中文描述: | 的1394b OHCI的山貓控制器 |

| 文件頁(yè)數(shù): | 51/104頁(yè) |

| 文件大?。?/td> | 461K |

| 代理商: | TSB82AA2I |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)當(dāng)前第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)第69頁(yè)第70頁(yè)第71頁(yè)第72頁(yè)第73頁(yè)第74頁(yè)第75頁(yè)第76頁(yè)第77頁(yè)第78頁(yè)第79頁(yè)第80頁(yè)第81頁(yè)第82頁(yè)第83頁(yè)第84頁(yè)第85頁(yè)第86頁(yè)第87頁(yè)第88頁(yè)第89頁(yè)第90頁(yè)第91頁(yè)第92頁(yè)第93頁(yè)第94頁(yè)第95頁(yè)第96頁(yè)第97頁(yè)第98頁(yè)第99頁(yè)第100頁(yè)第101頁(yè)第102頁(yè)第103頁(yè)第104頁(yè)

49

4.9

Bus Options Register

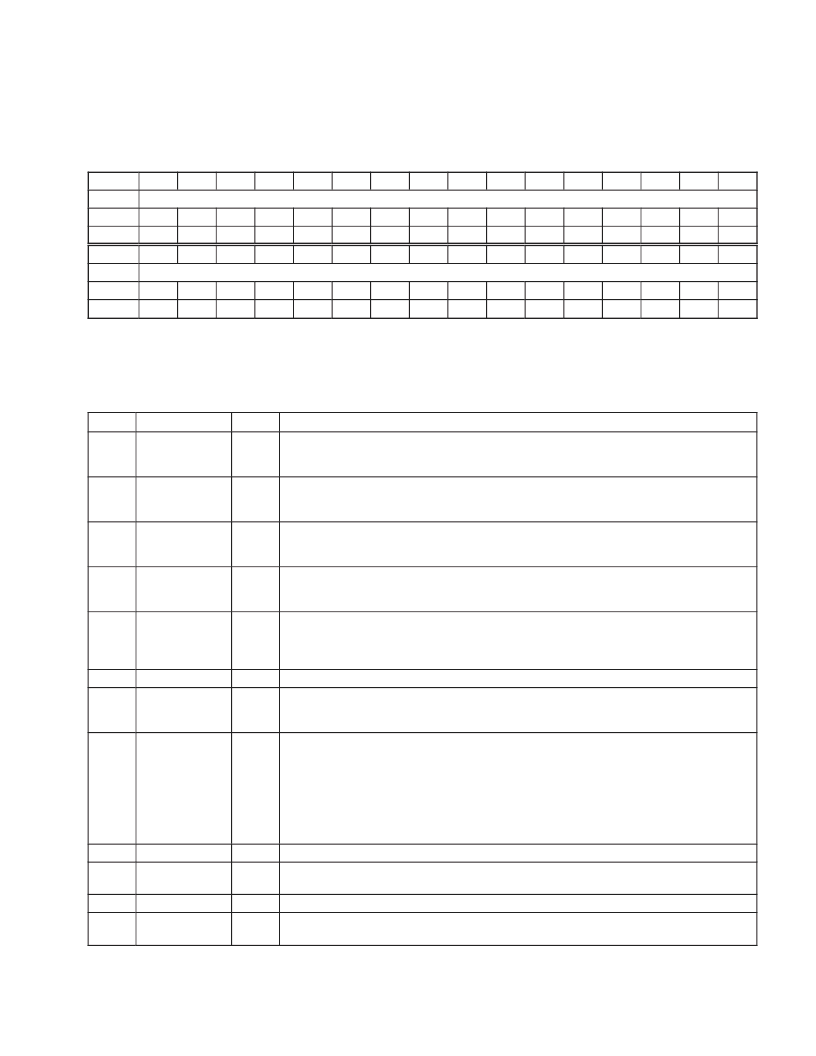

The bus options register externally maps to the second quadlet of the Bus_Info_Block. See Table 47 for a complete

description of the register contents.

Bit

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

16

Name

Bus options

Type

R/W

R/W

R/W

R/W

R/W

R

R

R

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

Default

X

X

X

X

0

0

0

0

X

X

X

X

X

X

X

X

Bit

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

Name

Bus options

Type

R/W

R/W

R/W

R/W

R

R

R

R

R/W

R/W

R

R

R

R

R

R

Default

1

0

1

1

0

0

0

0

X

X

0

0

0

0

1

0

Register:

Type:

Offset:

Default:

Bus options

Read/Write, Read-only

20h

X0XX B0X2h

Table 47. Bus Options Register Description

BIT

FIELD NAME

TYPE

DESCRIPTION

31

irmc

R/W

Isochronous resource-manager capable. IEEE 1394 bus-management field. Must be valid when bit 17

(linkEnable) in the host controller control register at OHCI offset 50h/54h (see Section 4.16,

Host

Controller Control Register

) is set to 1.

30

cmc

R/W

Cycle master capable. IEEE 1394 bus-management field. Must be valid when bit 17 (linkEnable) in the

host controller control register at OHCI offset 50h/54h (see Section 4.16,

Host Controller Control

Register

) is set to 1.

29

isc

R/W

Isochronous support capable. IEEE 1394 bus-management field. Must be valid when bit 17

(linkEnable) in the host controller control register at OHCI offset 50h/54h (see Section 4.16,

Host

Controller Control Register

) is set to 1.

28

bmc

R/W

Bus manager capable. IEEE 1394 bus-management field. Must be valid when bit 17 (linkEnable) in

the host controller control register at OHCI offset 50h/54h (see Section 4.16,

Host Controller Control

Register

) is set to 1.

27

pmc

R/W

Power-management capable. IEEE 1394 bus-management field. When bit 27 is set to 1, this indicates

that the node is power-management capable. Must be valid when bit 17 (linkEnable) in the host

controller control register at OHCI offset 50h/54h (see Section 4.16,

Host Controller Control Register

)

is set to 1.

2624

RSVD

R

Reserved. Bits 2624 return 0s when read.

2316

cyc_clk_acc

R/W

Cycle master clock accuracy, in parts per million. IEEE 1394 bus-management field. Must be valid

when bit 17 (linkEnable) in the host controller control register at OHCI offset 50h/54h (see Section 4.16,

Host Controller Control Register

) is set to 1.

1512

max_rec

R/W

Maximum request. IEEE 1394 bus-management field. Hardware initializes this field to indicate the

maximum number of bytes in a block request packet that is supported by the implementation. This

value, max_rec_bytes must be 512 or greater, and is calculated by 2^(max_rec + 1). Software may

change this field; however, this field must be valid at any time bit 17 (linkEnable) in the host controller

control register at OHCI offset 50h/54h (see Section 4.16,

Host Controller Control Register

) is set to

1. A received block write request packet with a length greater than max_rec_bytes may generate an

ack_type_error. This field is not affected by a software reset, and defaults to a value indicating

4096 bytes on a system (hardware) reset.

118

RSVD

R

Reserved. Bits 118 return 0s when read.

76

g

R/W

Generation counter. This field is incremented if any portion of the configuration ROM has been

incremented since the prior bus reset.

53

RSVD

R

Reserved. Bits 53 return 0s when read.

20

Lnk_spd

R

Link speed. This field returns 010, indicating that the link speeds of 100M bits/s, 200M bits/s, and

400M bits/s are supported.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| TSC2200EVM | TSC2200 Touch Screen Controller Evaluation Module(TSC2200觸摸屏控制器評(píng)估模塊) |

| TSC427CBA | Dual Power MOSFET Drivers |

| TSC427CPA | Dual Power MOSFET Drivers |

| TSC428CBA | Dual Power MOSFET Drivers |

| TSC426CBA | Dual Power MOSFET Drivers |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| TSB82AA2IPGE | 功能描述:接口 - 專用 OHCI-Lynx Controller RoHS:否 制造商:Texas Instruments 產(chǎn)品類型:1080p60 Image Sensor Receiver 工作電源電壓:1.8 V 電源電流:89 mA 最大功率耗散: 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:BGA-59 |

| TSB82AA2IPGEEP | 功能描述:1394 接口集成電路 Mil Enh 1394b OHCI- Lynx Cntrlr RoHS:否 制造商:Texas Instruments 類型:Link Layer Controller 工作電源電壓: 封裝 / 箱體:LQFP 封裝:Tray |

| TSB82AA2PGE | 功能描述:1394 接口集成電路 OHCI-Lynx Controller RoHS:否 制造商:Texas Instruments 類型:Link Layer Controller 工作電源電壓: 封裝 / 箱體:LQFP 封裝:Tray |

| TSB82AA2PGEG4 | 功能描述:1394 接口集成電路 OHCI-Lynx Controller RoHS:否 制造商:Texas Instruments 類型:Link Layer Controller 工作電源電壓: 封裝 / 箱體:LQFP 封裝:Tray |

| TSB82AA2ZGW | 功能描述:1394 接口集成電路 OHCI-Lynx Controller RoHS:否 制造商:Texas Instruments 類型:Link Layer Controller 工作電源電壓: 封裝 / 箱體:LQFP 封裝:Tray |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。