- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄97867 > DS2196LN (DALLAS SEMICONDUCTOR) DATACOM, FRAMER, PQFP100 PDF資料下載

參數(shù)資料

| 型號: | DS2196LN |

| 廠商: | DALLAS SEMICONDUCTOR |

| 元件分類: | Digital Transmission Controller |

| 英文描述: | DATACOM, FRAMER, PQFP100 |

| 封裝: | LQFP-100 |

| 文件頁數(shù): | 136/160頁 |

| 文件大小: | 559K |

| 代理商: | DS2196LN |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁第107頁第108頁第109頁第110頁第111頁第112頁第113頁第114頁第115頁第116頁第117頁第118頁第119頁第120頁第121頁第122頁第123頁第124頁第125頁第126頁第127頁第128頁第129頁第130頁第131頁第132頁第133頁第134頁第135頁當(dāng)前第136頁第137頁第138頁第139頁第140頁第141頁第142頁第143頁第144頁第145頁第146頁第147頁第148頁第149頁第150頁第151頁第152頁第153頁第154頁第155頁第156頁第157頁第158頁第159頁第160頁

DS2196

77 of 160

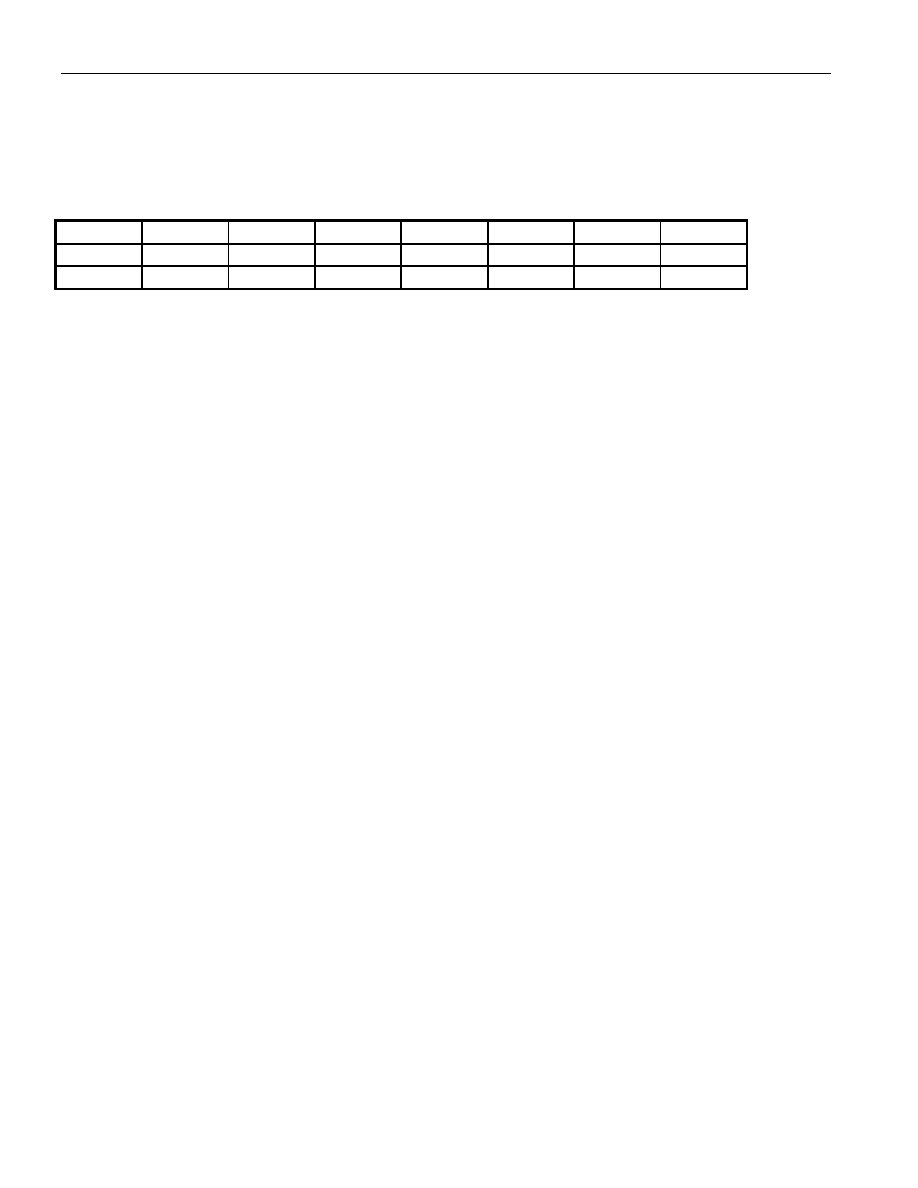

RMR1A/RMR2A/RMR3A: RECEIVE MARK REGISTERS FRAMER A

(Address = 2D to 2F Hex)

RMR1B/RMR2B/RMR3B: RECEIVE MARK REGISTERS FRAMER B

(Address = CD to CF Hex)

(MSB)

(LSB)

CH8

CH7

CH6

CH5

CH4

CH3

CH2

CH1

RMR1

CH16

CH15

CH14

CH13

CH12

CH11

CH10

CH9

RMR2

CH24

CH23

CH22

CH21

CH20

CH19

CH18

CH17

RMR3

SYMBOLS

POSITIONS

NAME AND DESCRIPTION

CH1-24

RMR1.0-3.7

Receive Channel Mark Control Bits

0 =do not affect the receive data associated with this channel

1 = replace the receive data associated with this channel with

either the idle code or the digital milliwatt code (depends on the

RCR2.7 bit)

12

PROGRAMMABLE IN–BAND CODE GENERATION AND DETECTION

Each framer in the DS2196 has the ability to generate and detect a repeating bit pattern that is from one to

8 bits and 16 bits in length. To transmit a pattern, the user will load the pattern to be sent into the

Transmit Code Definition (TCD1&TCD2) registers and select the proper length of the pattern by setting

the TC0 and TC1 bits in the In–Band Code Control (IBCC) register. When generating a 1, 2, 4, 8 or

16 bit pattern both transmit code definition registers (TCD1&TCD2) must be filled with the proper code.

Generation of a 3, 5, 6 and 7 bit pattern only requires TCD1 to be filled. Once this is accomplished, the

pattern will be transmitted as long as the TLOOP control bit (CCR3.1) is enabled. Normally (unless the

transmit formatter is programmed to not insert the F–bit position) the framer will overwrite the repeating

pattern once every 193 bits to allow the F–bit position to be sent. See Figure 21-7 for more details. As an

example, if the user wished to transmit the standard “l(fā)oop up” code for Channel Service Units which is a

repeating pattern of ...10000100001... then 80h would be loaded into TCD1 and the length would set to

5 bits.

Each framer can detect three separate repeating patterns. Typically, two of the detectors are used for

“l(fā)oop up” and “l(fā)oop down” code detection. The user will program the codes to be detected in the

Receive Up Code Definition (RUPCD1 & RUPCD2) registers and the Receive Down Code Definition

(RDNCD1 & RDNCD2) registers and the length of each pattern will be selected via the IBCC register.

There is a third detector (Spare) and it is defined and controlled via the RSCD1/RSCD2 and RSCC

registers. When detecting an 8 or 16 bit pattern both receive code definition registers must be filled with

the proper code. For 8 bit patterns both receive code definition registers will be filled with the same

value. Detection of a 1, 2, 3, 4, 5, 6 and 7 bit pattern only requires the first receive code definition

register to be filled. A third or spare detector is available for user definition. The framer will detect

repeating pattern codes in both framed and unframed circumstances with bit error rates as high as 10E–2.

The detectors are capable of handling both F-bit inserted and F-bit overwrite patterns. Writing the least

significant byte of receive code definition register resets the integration period for that detector. The code

detector has a nominal integration period of 30 ms. Hence, after about 30 ms of receiving a valid code,

the proper status bit (LUP at SR1A/B.7 , LDN at SR1A/B.6 and LSPARE at SR1A/B.4 ) will be set to a

1. Normally codes are sent for a period of 5 seconds. It is recommend that the software poll the framer

every 50 ms to 1000 ms until 5 seconds has elapsed to insure that the code is continuously present.

IBCCA: IN–BAND CODE CONTROL REGISTER FRAMER A

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| DS21FF44 | DATACOM, FRAMER, PBGA300 |

| DS21FF44N | DATACOM, FRAMER, PBGA300 |

| DS21FT40N | DATACOM, FRAMER, PBGA300 |

| DS21FT40 | DATACOM, FRAMER, PBGA300 |

| DS21FT42 | DATACOM, FRAMER, PBGA300 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| DS2196LN+ | 功能描述:網(wǎng)絡(luò)控制器與處理器 IC T1 Dual Framer LIU RoHS:否 制造商:Micrel 產(chǎn)品:Controller Area Network (CAN) 收發(fā)器數(shù)量: 數(shù)據(jù)速率: 電源電流(最大值):595 mA 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:PBGA-400 封裝:Tray |

| DS219T | 功能描述:烙鐵 DESOLDERING HEAD RoHS:否 制造商:Weller 產(chǎn)品:Soldering Stations 類型:Digital, Iron, Stand, Cleaner 瓦特:50 W 最大溫度:+ 850 F 電纜類型:US Cord Included |

| DS21E352 | 功能描述:網(wǎng)絡(luò)控制器與處理器 IC RoHS:否 制造商:Micrel 產(chǎn)品:Controller Area Network (CAN) 收發(fā)器數(shù)量: 數(shù)據(jù)速率: 電源電流(最大值):595 mA 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:PBGA-400 封裝:Tray |

| DS21E352N | 功能描述:網(wǎng)絡(luò)控制器與處理器 IC RoHS:否 制造商:Micrel 產(chǎn)品:Controller Area Network (CAN) 收發(fā)器數(shù)量: 數(shù)據(jù)速率: 電源電流(最大值):595 mA 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:PBGA-400 封裝:Tray |

| DS21E354 | 功能描述:網(wǎng)絡(luò)控制器與處理器 IC RoHS:否 制造商:Micrel 產(chǎn)品:Controller Area Network (CAN) 收發(fā)器數(shù)量: 數(shù)據(jù)速率: 電源電流(最大值):595 mA 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:PBGA-400 封裝:Tray |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。