- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄382721 > UDA1352HL (NXP SEMICONDUCTORS) 48 kHz IEC 60958 audio DAC PDF資料下載

參數(shù)資料

| 型號: | UDA1352HL |

| 廠商: | NXP SEMICONDUCTORS |

| 元件分類: | 消費家電 |

| 英文描述: | 48 kHz IEC 60958 audio DAC |

| 中文描述: | SPECIALTY CONSUMER CIRCUIT, PQFP48 |

| 封裝: | 7 X 7 MM, 1.40 MM HEIGHT, PLASTIC, MS-026, SOT-313-2, LQFP-48 |

| 文件頁數(shù): | 22/64頁 |

| 文件大小: | 262K |

| 代理商: | UDA1352HL |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁當(dāng)前第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁

2003 Mar 25

22

Philips Semiconductors

Preliminary specification

48 kHz IEC 60958 audio DAC

UDA1352HL

10.3

Byte transfer

Each byte (8 bits) is transferred with the MSB first

(see Table 10).

Table 10

Byte transfer

10.4

Data transfer

A device generating a message is a transmitter, a device

receiving a message is the receiver. The device that

controls the message is the master and the devices which

are controlled by the master are the slaves.

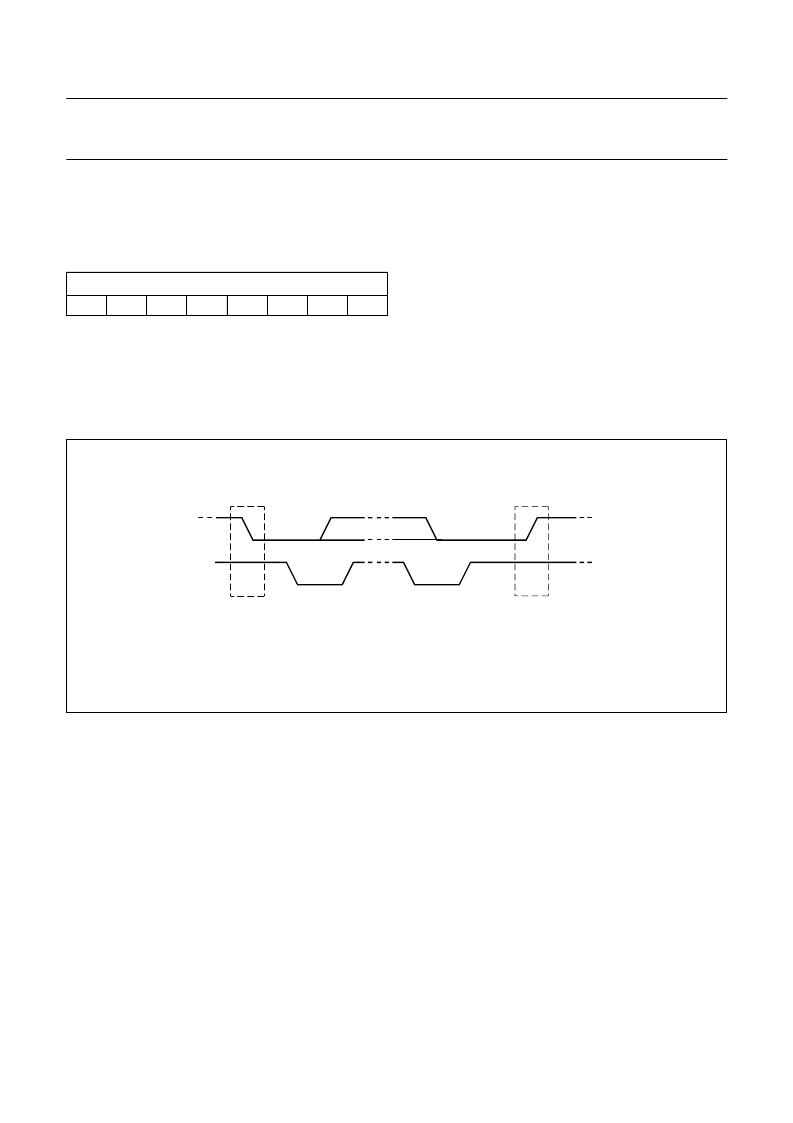

10.5

Start and stop conditions

Both data and clock lines will remain HIGH when the bus

is not busy. A HIGH-to-LOW transition of the data line,

while the clock is HIGH, is defined as a start condition (S);

see Fig.9. A LOW-to-HIGH transition of the data line while

the clock is HIGH is defined as a stop condition (P).

MSB

BIT NUMBER

LSB

7

6

5

4

3

2

1

0

handbook, full pagewidth

MBC622

SDA

SCL

P

STOP condition

SDA

SCL

S

START condition

Fig.9 START and STOP conditions on the I

2

C-bus.

10.6

Acknowledgment

There is no limit to the number of data bits transferred from

the transmitter to receiver between the start and stop

conditions. Each byte of eight bits is followed by one

acknowledge bit (see Fig.10). At the acknowledge bit, the

data line is released by the master and the master

generates an extra acknowledge related clock pulse.

A slave receiver which is addressed must generate an

acknowledge after receiving each byte. Also a master

must generate an acknowledge after receiving each byte

that has been clocked out of the slave transmitter.

The acknowledging device must pull-down the SDA line

during the HIGH period of the acknowledge clock pulse so

that the SDA line is stable LOW. Set-up and hold times

must be taken into account. A master receiver must signal

an end of data to the transmitter by not generating an

acknowledge on the last byte that has been clocked out of

the slave. In this event, the transmitter must leave the data

line HIGH to enable the master to generate a stop

condition.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| UDA1360 | Low-voltage low-power stereo audio ADC |

| UDA1360TS | Low-voltage low-power stereo audio ADC |

| UDA1361 | 96 kHz sampling 24-bit stereo audio ADC |

| UDA1380 | Stereo audio coder-decoder for MD, CD and MP3 |

| UDA1380TT | Stereo audio coder-decoder for MD, CD and MP3 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| UDA1352TS | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:48 kHz IEC 60958 audio DAC |

| UDA1352TS/N3 | 制造商:NXP Semiconductors 功能描述:IC DAC AUDIO 48KHZ 28-SSOP 制造商:NXP Semiconductors 功能描述:IC, DAC, AUDIO, 48KHZ, 28-SSOP, Resolution (Bits):20bit, Input Channel Type:Seri |

| UDA1352TS/N3,112 | 功能描述:音頻數(shù)/模轉(zhuǎn)換器 IC DAC 2CH Interpolatio Filter 28-Pin RoHS:否 制造商:Texas Instruments 轉(zhuǎn)換器數(shù)量: 分辨率:16 bit 接口類型:I2S, UBS 轉(zhuǎn)換速率: 信噪比:98 dB 工作電源電壓:5 V DAC 輸出端數(shù)量:2 工作溫度范圍:- 25 C to + 85 C 電源電流:23 mA 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:TQFP-32 封裝:Reel |

| UDA1352TS/N3,118 | 功能描述:數(shù)模轉(zhuǎn)換器- DAC DAC 2CH Interpolatio Filter 28-Pin RoHS:否 制造商:Texas Instruments 轉(zhuǎn)換器數(shù)量:1 DAC 輸出端數(shù)量:1 轉(zhuǎn)換速率:2 MSPs 分辨率:16 bit 接口類型:QSPI, SPI, Serial (3-Wire, Microwire) 穩(wěn)定時間:1 us 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:SOIC-14 封裝:Tube |

| UDA1352TS/N3112 | 制造商:Rochester Electronics LLC 功能描述: 制造商:NXP 功能描述: 制造商:NXP Semiconductors 功能描述: |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。