- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄384032 > TVP3026-175M (Texas Instruments, Inc.) Video Interface PALETTE Exract(組合像素模式視頻接口調(diào)色器) PDF資料下載

參數(shù)資料

| 型號: | TVP3026-175M |

| 廠商: | Texas Instruments, Inc. |

| 英文描述: | Video Interface PALETTE Exract(組合像素模式視頻接口調(diào)色器) |

| 中文描述: | 視頻接口調(diào)色板Exract(組合像素模式視頻接口調(diào)色器) |

| 文件頁數(shù): | 23/107頁 |

| 文件大小: | 707K |

| 代理商: | TVP3026-175M |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁當(dāng)前第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁第107頁

2–9

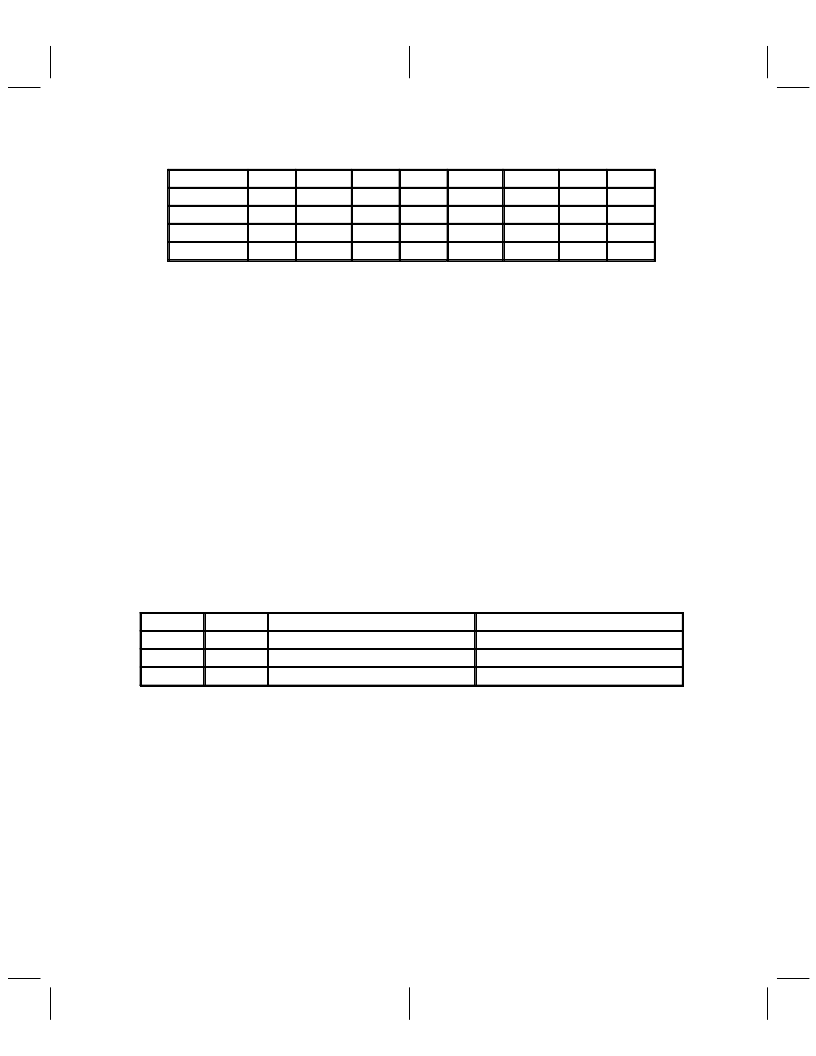

Table 2–10. Pixel Clock PLL Registers

REGISTER

BIT 7

BIT 6

BIT 5

BIT 4

BIT 3

BIT 2

BIT 1

BIT 0

N value

1

1

N5

N4

N3

N2

N1

N0

M value

0

0

M5

M4

M3

M2

M1

M0

P value

PLLEN

PCLKEN

1

1

LFORCE

PFORCE

P1

P0

Status

X

LOCK

X

X

X

X

X

X

X = do not care

2.4.1.1

The pixel clock PLL frequency may be selected using the PLL select inputs PLLSEL(1,0) as shown in

Table 2–11. The first two selections are fixed frequency settings for standard VGA operation. Use of a

standard 14.31818 MHz crystal is assumed. When PLLSEL1 is set to 1, the frequency specified by the pixel

clock PLL N-, M-, and P-value registers is selected. When PLLSEL1 is set to 1 at power up or during a

software reset, the pixel clock PLL N-, M-, and P-value registers default to settings for 25.057 MHz, but with

the PLL disabled. Therefore, the system must reset PLLSEL(1,0) to 0x when a software reset occurs or the

pixel clock PLL and RCLK stops oscillating.

Pixel Clock PLL Frequency Selection

The frequency select inputs also apply to the loop clock PLL. When a fixed frequency is selected

(PLLSEL(1,0) = 0x), the loop clock PLL passes the dot clock frequency to the RCLK multiplexer. Internal

feedback is used, no external signal path from RCLK to LCLK is required. When PLLSEL1 is 1, the frequency

specified by the loop clock PLL N-, M-, and P-value registers is selected.

For VGA Mode 1, the pixel clock PLL is normally selected as the dot clock source (CSR = 0x05) and the

RCLK terminal passes the loop clock PLL output (MCK5 = 1). Then, when PLLSEL(1,0) changes between

a programmed frequency and a fixed frequency, the loop clock PLL automatically changes with it. The loop

clock PLL does not require reprogramming.

For VGA Mode 2, CLK0 should be selected as the dot clock source (CSR = 0x07) and the RCLK terminal

should pass the pixel clock PLL output (MCK5 = 0). In this case, the loop clock PLL should be disabled (bit

P7 = 0) since its output is not used.

Table 2–11. Pixel Clock PLL Frequency Selection

PLLSEL1

PLLSEL0

PIXEL CLOCK PLL FREQUENCY

LOOP CLOCK PLL FREQUENCY

0

0

25.057 MHz

Pass DOT CLOCK, internal feedback

0

1

28.636 MHz

Pass DOT CLOCK, internal feedback

1

X

Programmed by pixel clock PLL registers

Programmed by loop clock PLL registers

X = do not care

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| TVP3026-220 | Video Interface PALETTE Exract(組合像素模式視頻接口調(diào)色器) |

| TVP3026-250 | Video Interface PALETTE Exract(組合像素模式視頻接口調(diào)色器) |

| TX24 | 60.8 MM 5 X 8 DOT MATRIX DISPLAYS |

| TXB0102DCTR | 2-BIT BIDIRECTIONAL VOLTAGE-LEVEL TRANSLATOR WITH AUTO DIRECTION SENSING AND 【15-kV ESD PROTECTION |

| TXB0102DCTT | 2-BIT BIDIRECTIONAL VOLTAGE-LEVEL TRANSLATOR WITH AUTO DIRECTION SENSING AND 【15-kV ESD PROTECTION |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| TVP3026-175MDN | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Video DAC with Color Palette (RAMDAC) |

| TVP3026-175MHFG | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Video DAC with Color Palette (RAMDAC) |

| TVP3026-175MHFGB | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Video DAC with Color Palette (RAMDAC) |

| TVP3026-175PCE | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| TVP3026-220AMDN | 制造商:TI 制造商全稱:Texas Instruments 功能描述:Video Interface Palette |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。