- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄383838 > ST20GP1 MAX 7000 CPLD 256 MC 208-PQFP PDF資料下載

參數(shù)資料

| 型號: | ST20GP1 |

| 英文描述: | MAX 7000 CPLD 256 MC 208-PQFP |

| 中文描述: | GPS處理器 |

| 文件頁數(shù): | 32/116頁 |

| 文件大?。?/td> | 1107K |

| 代理商: | ST20GP1 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁當前第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁第107頁第108頁第109頁第110頁第111頁第112頁第113頁第114頁第115頁第116頁

ST20-GP1

32/116

On start-up, the

Mask

register is initialized to zero’s, thus all interrupts are disabled, both globally

and individually. When a 1 is written to the

GlobalEnable

bit, the individual interrupt bits are still

disabled and must also have a 1 individually written to the

InterruptEnable

bit to enable the

respective interrupt.

The

Mask

register is mapped onto two additional addresses so that bits can be set or cleared

individually.

Set_Mask

(address ‘interrupt base address + #C4’) allows bits to be set individually. Writing a ‘1’ in

this register sets the corresponding bit in the

Mask

register, a ‘0’ leaves the bit unchanged.

Clear_Mask

(address ‘interrupt base address + #C8’) allows bits to be cleared individually. Writing

a ‘1’ in this register resets the corresponding bit in the

Mask

register, a ‘0’ leaves the bit

unchanged.

Pending register

The

Pending

register contains a bit per interrupt with each bit controlled by the corresponding

interrupt. A read can be used to examine the state of the interrupt controller while a write can be

used to explicitly trigger an interrupt.

A bit is set when the triggering condition for an interrupt is met. All bits are independent so that

several bits can be set in the same cycle. Once a bit is set, a further triggering condition will have

no effect. The triggering condition is independent of the

Mask

register.

The highest priority interrupt bit is reset once the interrupt controller has made an interrupt request

to the CPU.

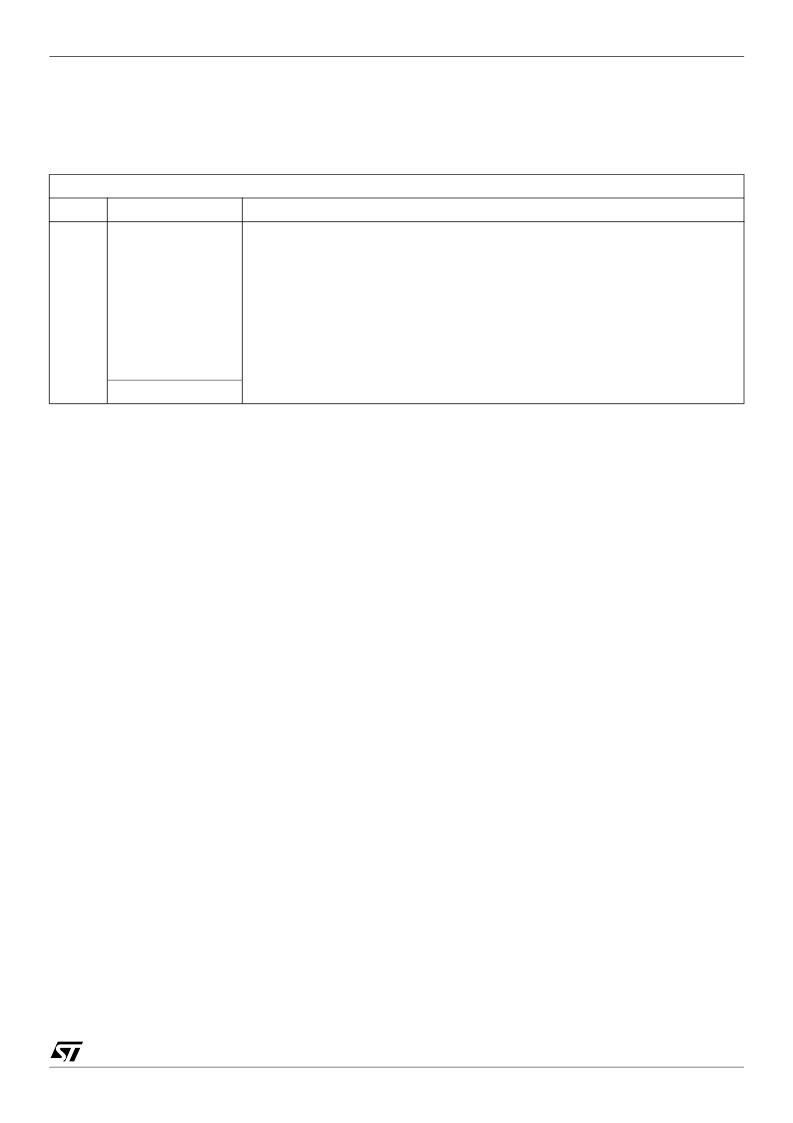

Mask

Interrupt controller base address + #C0

Read/Write

Bit

Bit field

Function

0

Interrupt0Enable

When set to 1, interrupt 0 is enabled. When 0, interrupt 0 is disabled.

1

Interrupt1Enable

When set to 1, interrupt 1 is enabled. When 0, interrupt 1 is disabled.

2

Interrupt2Enable

When set to 1, interrupt 2 is enabled. When 0, interrupt 2 is disabled.

3

Interrupt3Enable

When set to 1, interrupt 3 is enabled. When 0, interrupt 3 is disabled.

4

Interrupt4Enable

When set to 1, interrupt 4 is enabled. When 0, interrupt 4 is disabled.

16

GlobalEnable

When set to 1, the setting of the interrupt is determined by the specific

InterruptEn-

able

bit. When 0, all interrupts are disabled.

15:5

RESERVED. Write 0.

Table 5.3

Mask

register format

相關PDF資料 |

PDF描述 |

|---|---|

| ST20GP6 | MAX 7000 CPLD 256 MC 208-RQFP |

| ST25C02AB1 | IC FLEX 6000 FPGA 16K 144-TQFP |

| ST25C02AB6 | Stratix FPGA 25K FBGA-672 |

| ST25C02AM1 | IC ACEX 1K FPGA 100K 208-PQFP |

| ST25C02AM6 | Cyclone II FPGA 20K FBGA-256 |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| ST20-GP1 | 制造商:STMICROELECTRONICS 制造商全稱:STMicroelectronics 功能描述:GPS PROCESSOR |

| ST20GP1X33S | 制造商:STMICROELECTRONICS 制造商全稱:STMicroelectronics 功能描述:GPS PROCESSOR |

| ST20GP6 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:GPS PROCESSOR |

| ST20-GP6 | 制造商:STMICROELECTRONICS 制造商全稱:STMicroelectronics 功能描述:GPS PROCESSOR |

| ST20GP6CT33S | 制造商:STMICROELECTRONICS 制造商全稱:STMicroelectronics 功能描述:GPS PROCESSOR |

發(fā)布緊急采購,3分鐘左右您將得到回復。