- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄371670 > 83C795 (SMSC Corporation) Ethernet System Controller PDF資料下載

參數(shù)資料

| 型號: | 83C795 |

| 廠商: | SMSC Corporation |

| 英文描述: | Ethernet System Controller |

| 中文描述: | 以太網(wǎng)系統(tǒng)控制器 |

| 文件頁數(shù): | 78/136頁 |

| 文件大小: | 1996K |

| 代理商: | 83C795 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁當前第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁第107頁第108頁第109頁第110頁第111頁第112頁第113頁第114頁第115頁第116頁第117頁第118頁第119頁第120頁第121頁第122頁第123頁第124頁第125頁第126頁第127頁第128頁第129頁第130頁第131頁第132頁第133頁第134頁第135頁第136頁

7.0

The LAN Controller consists of 3 basic blocks:

DMA controller, transmitter, and receiver. Each of

these blocks consists of sub-sections. The DMA

controller includes a memory interface unit, control

registers, and a micro-coded sequencer that

handles data buffering for the transmitter and

receiver sections.

LAN CONTROLLER OVERVIEW

The transmitter block has a MAC (Media Access

Control) section that performs the IEEE 802.3

transmission protocol and a Physical Layer

Interface (PLI) section that does Manchester

encoding and drives the cables.

The receiver block has a MAC section that performs

the 802.3 reception protocol and a PLI section that

converts line level differential signals to internal

logic signals while doing clock recovery, and

manchester decoding.

7.1

The DMA controller handles data movement

between the FIFOs and buffer memory for

transmission and reception of frames. All DMA data

traffic is 8-bit wide. One DMA controller is shared

between the transmit and receive functions. The

controller groups memory transfers into bursts of 8

bytes for both transmit and receive functions. The

DMA controller always accesses memory by doing

two single-byte transfers in a row. The burst size

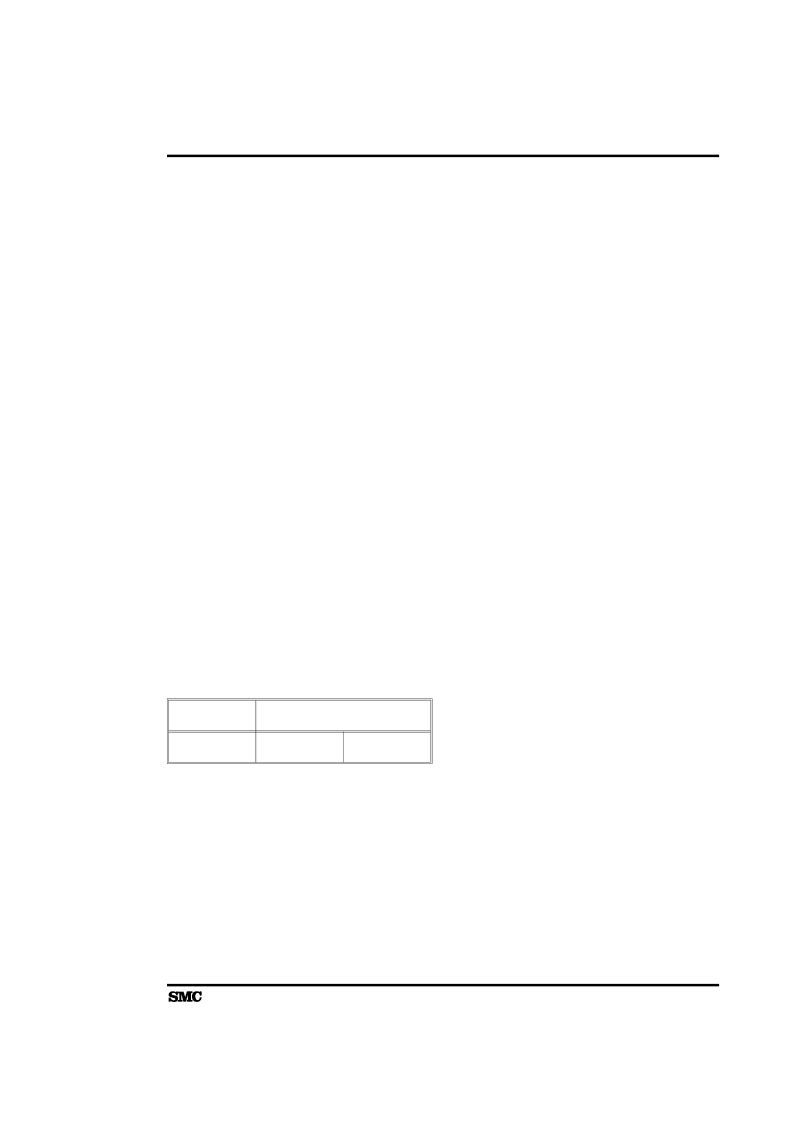

and its trigger levels are shown in Table 7-1.

DMA CONTROLLER

BURST

TRIGGER LEVEL

RX TX

8 bytes

R

≥

8

T

≤

8

TABLE 7-1. DMA BURST LENGTH FIELD

Though internally 8 bits wide, the DMA controller

generates 16-bit addresses. It accesses memory in

2 cycles of the chip’s master clock (per byte).

When conducting a loop-back test, this controller

can handle full-duplex buffering of full length frames

at serial data rates up to 10 Mbps. It does not handle

the general case of independent (concurrent)

transmit and reception processes.

7.1.1

These latches are used to match up the internal

8-bit data path with the external data bus. Assembly

latches build a 16-bit word out of two 8-bit words or

supplies the consecutive bytes when interfacing to

an 8-bit bus. Disassembly latches perform the

inverse function. These are used during DMA

operations and are bypassed when the chip’s

registers are written or read.

Assembly and Disassembly Latches

7.1.2

The memory interface unit (MIU) transfers data

from buffer memory to the internal disassembly

latches and from the internal assembly latches to

buffer memory. It is a part of the DMA controller.

This block generates the memory strobes

(RAMOE, RAMWR) when the DMA is accessing

the buffer RAM.

Memory Interface Unit

MIU operation is initiated by the DMA controller

after it sets up the address for the transfer and puts

outgoing data (receiver functions) into the

assembly latches. The MIU then performs the

memory transfer in the next time slot assigned to

the DMA.

The basic DMA cycles are in Figure 7-1. Real

details can be found in the AC timing section.

LAN CONTROLLER OVERVIEW

83C795

65

相關PDF資料 |

PDF描述 |

|---|---|

| 84063 | The Constituents of Semiconductor Components |

| 8406601QA | CMOS Programmable Peripheral Interface |

| 8406601XA | CMOS Programmable Peripheral Interface |

| 8406602XA | CMOS Programmable Peripheral Interface |

| 8406602QA | CMOS Programmable Peripheral Interface |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| 83C800-009 | 制造商:DRS 功能描述: |

| 83C825EQFP | 制造商:SMSC 功能描述: |

| 83C845 | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:Microcontrollers for TV and video MTV |

| 83C851 | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:CMOS single-chip 8-bit microcontroller with on-chip EEPROM |

| 83C852DIE | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:8-Bit Microcontroller |

發(fā)布緊急采購,3分鐘左右您將得到回復。