- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄371436 > 28F640C3 (Intel Corp.) 3 Volt Advanced Boot Block Flash Memory(3 V 高級快速引導(dǎo)塊閃速存儲器) PDF資料下載

參數(shù)資料

| 型號: | 28F640C3 |

| 廠商: | Intel Corp. |

| 英文描述: | 3 Volt Advanced Boot Block Flash Memory(3 V 高級快速引導(dǎo)塊閃速存儲器) |

| 中文描述: | 3伏高級啟動塊閃存(3伏高級快速引導(dǎo)塊閃速存儲器) |

| 文件頁數(shù): | 23/70頁 |

| 文件大小: | 894K |

| 代理商: | 28F640C3 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁當(dāng)前第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁

28F800C3, 28F160C3, 28F320C3, 28F640C3

3UHOLPLQDU\

17

3.3.4

Reading a Block’s Lock Status

The lock status of every block can be read in the configuration read mode of the device. To enter

this mode, write 90H to the device. Subsequent reads at Block Address + 00002 will output the

lock status of that block. The lock status is represented by DQ

0

and DQ

1

. DQ

0

indicates the Block

Lock/Unlock status and is set by the Lock command and cleared by the Unlock command. It is also

automatically set when entering Lock-Down. DQ

1

indicates Lock-Down status and is set by the

Lock-Down command. It cannot be cleared by software, only by device reset or power-down.

3.3.5

Locking Operations during Erase Suspend

Changes to block lock status can be performed during an erase suspend by using the standard

locking command sequences to unlock, lock, or lock-down a block. This is useful in the case when

another block needs to be updated while an erase operation is in progress.

To change block locking during an erase operation, first write the erase suspend command (B0H),

then check the status register until it indicates that the erase operation has been suspended. Next

write the desired lock command sequence to a block and the lock status will be changed. After

completing any desired lock, read, or program operations, resume the erase operation with the

Erase Resume command (D0H).

If a block is locked or locked-down during a suspended erase of the same block, the locking status

bits will be changed immediately, but when the erase is resumed, the erase operation will complete.

Locking operations cannot be performed during a program suspend. Refer to

Appendix A

for

detailed information on which commands are valid during erase suspend.

3.3.6

Status Register Error Checking

Using nested locking or program command sequences during erase suspend can introduce

ambiguity into status register results.

Since locking changes are performed using a two cycle command sequence, e.g., 60H followed by

01H to lock a block, following the Configuration Setup command (60H) with an invalid command

will produce a lock command error (SR.4 and SR.5 will be set to 1) in the status register. If a lock

command error occurs during an erase suspend, SR.4 and SR.5 will be set to 1 and will remain at 1

after the erase is resumed. When erase is complete, any possible error during the erase cannot be

detected via the status register because of the previous locking command error.

A similar situation happens if an error occurs during a program operation error nested within an

erase suspend.

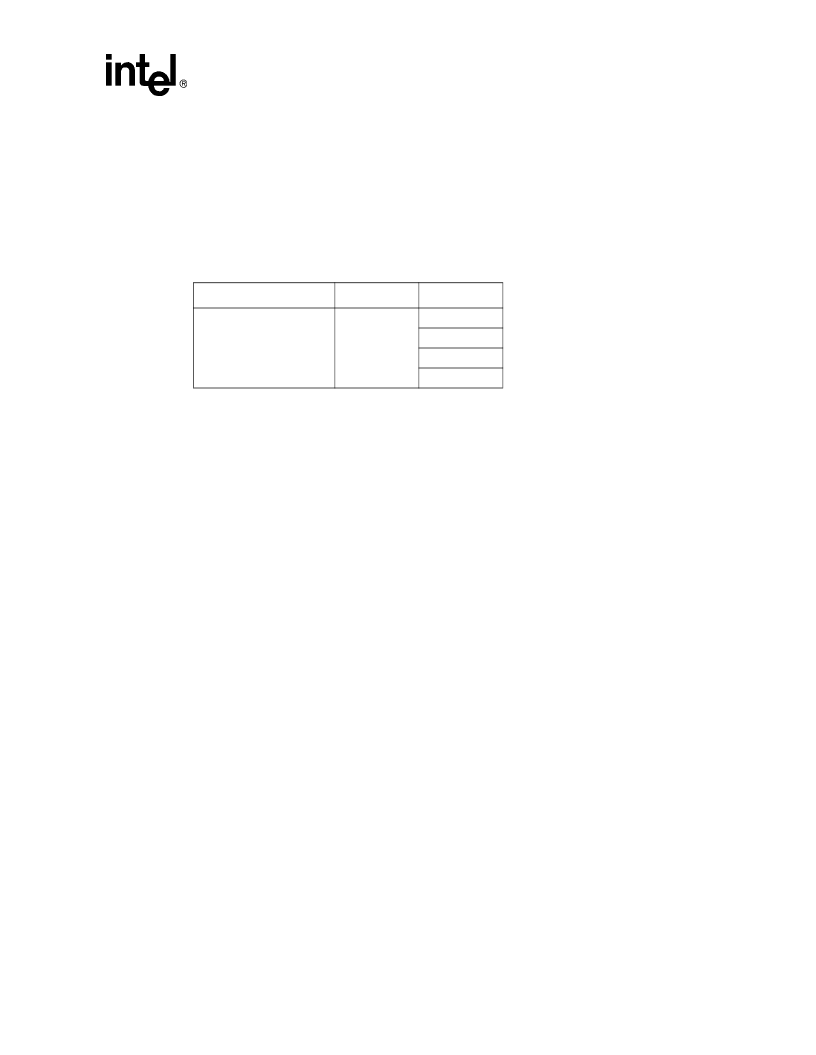

Table 8. Block Lock Status

Item

Address

Data

Block Lock Configuration

XX002

LOCK

Block Is Unlocked

DQ

0

= 0

Block Is Locked

DQ

0

= 1

Block Is Locked-Down

DQ

1

= 1

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| 28F640J3C-120 | Intel StrataFlash Memory (J3) |

| 28LV64A | 64K (8K x 8) Low Voltage CMOS EEPROM(低壓,64K位, CMOS 并行EEPROM) |

| 28M0U | 60V 300mA MONOLITHIC DIODE ARRAY |

| 28M0DC | 60V 300mA MONOLITHIC DIODE ARRAY |

| 28M0DS | 60V 300mA MONOLITHIC DIODE ARRAY |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| 28F640C3BC80 | 制造商: 功能描述: 制造商:undefined 功能描述: |

| 28F640J3C120 | 制造商: 功能描述: 制造商:undefined 功能描述: |

| 28F640J3C-120 | 制造商: 功能描述: 制造商:undefined 功能描述: |

| 28F640J3D75 | 制造商:Intel 功能描述: 制造商: 功能描述: 制造商:undefined 功能描述: |

| 28F640J5 | 制造商:INTEL 制造商全稱:Intel Corporation 功能描述:5 Volt Intel StrataFlash? Memory |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。