- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄371436 > 28F640C3 (Intel Corp.) 3 Volt Advanced Boot Block Flash Memory(3 V 高級快速引導(dǎo)塊閃速存儲器) PDF資料下載

參數(shù)資料

| 型號: | 28F640C3 |

| 廠商: | Intel Corp. |

| 英文描述: | 3 Volt Advanced Boot Block Flash Memory(3 V 高級快速引導(dǎo)塊閃速存儲器) |

| 中文描述: | 3伏高級啟動塊閃存(3伏高級快速引導(dǎo)塊閃速存儲器) |

| 文件頁數(shù): | 21/70頁 |

| 文件大小: | 894K |

| 代理商: | 28F640C3 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁當(dāng)前第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁

28F800C3, 28F160C3, 28F320C3, 28F640C3

3UHOLPLQDU\

15

NOTE:

A Command Sequence Error is indicated when both SR.4, SR.5 and SR.7 are set.

3.3

Flexible Block Locking

Intel 3 Volt Advanced+ Boot Block products offer an instant, individual block locking scheme that

allows any block to be locked or unlocked with no latency, enabling instant code and data

protection.

This locking scheme offers two levels of protection. The first level allows software-only control of

block locking (useful for data blocks that change frequently), while the second level requires

hardware interaction before locking can be changed (useful for code blocks that change

infrequently).

The following sections will discuss the operation of the locking system. The term “state [XYZ]”

will be used to specify locking states; e.g., “state [001],” where X = value of WP#, Y = bit DQ

1

of

the Block Lock status register, and Z = bit DQ

0

of the Block Lock status register.

Table 9, “Block

Locking State Transitions” on page 18

defines all of these possible locking states.

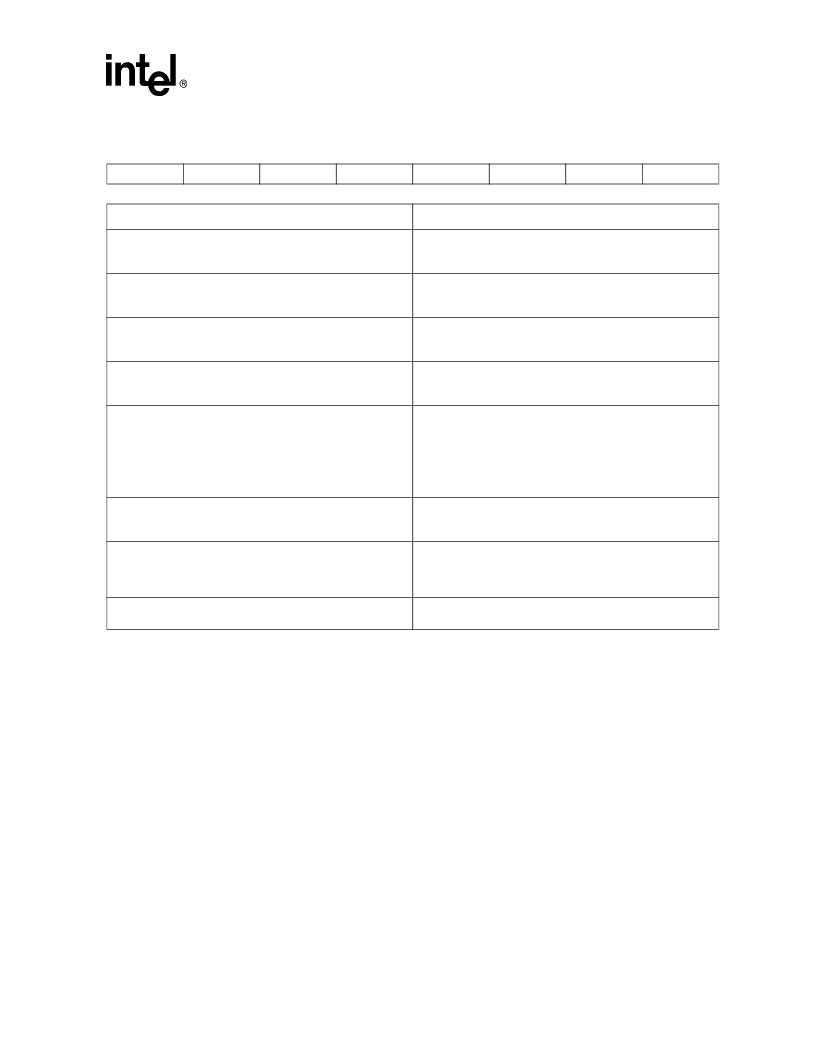

Table 7. Status Register Bit Definition

WSMS

ESS

ES

PS

VPPS

PSS

BLS

R

7

6

5

4

3

2

1

0

NOTES:

SR.7 WRITE STATE MACHINE STATUS (WSMS)

1 = Ready

0 = Busy

Check Write State Machine bit first to determine Word Program

or Block Erase completion, before checking Program or Erase

Status bits.

SR.6 = ERASE-SUSPEND STATUS (ESS)

1 = Erase Suspended

0 = Erase In Progress/Completed

When Erase Suspend is issued, WSM halts execution and sets

both WSMS and ESS bits to “1.” ESS bit remains set to “1” until

an Erase Resume command is issued.

SR.5 = ERASE STATUS (ES)

1 = Error In Block Erase

0 = Successful Block Erase

When this bit is set to “1,” WSM has applied the max. number

of erase pulses to the block and is still unable to verify

successful block erasure.

SR.4 = PROGRAM STATUS (PS)

1 = Error in Programming

0 = Successful Programming

When this bit is set to “1,” WSM has attempted but failed to

program a word/byte.

SR.3 = V

PP

STATUS (VPPS)

1 = V

PP

Low Detect, Operation Abort

0 = V

PP

OK

The V

PP

status bit does not provide continuous indication of

V

PP

level. The WSM interrogates V

PP

level only after the

Program or Erase command sequences have been entered,

and informs the system if V

PP

has not been switched on. The

V

PP

is also checked before the operation is verified by the

WSM. The V

PP

status bit is not guaranteed to report accurate

feedback between V

PPLK

and V

PP1

Min.

SR.2 = PROGRAM SUSPEND STATUS (PSS)

1 = Program Suspended

0 = Program in Progress/Completed

When Program Suspend is issued, WSM halts execution and

sets both WSMS and PSS bits to “1.” PSS bit remains set to “1”

until a Program Resume command is issued.

SR.1 = BLOCK LOCK STATUS

1 = Prog/Erase attempted on a locked

block; Operation aborted.

0 = No operation to locked blocks

If a program or erase operation is attempted to one of the

locked blocks, this bit is set by the WSM. The operation

specified is aborted and the device is returned to read status

mode.

SR.0 = RESERVED FOR FUTURE ENHANCEMENTS (R)

This bit is reserved for future use and should be masked out

when polling the status register.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| 28F640J3C-120 | Intel StrataFlash Memory (J3) |

| 28LV64A | 64K (8K x 8) Low Voltage CMOS EEPROM(低壓,64K位, CMOS 并行EEPROM) |

| 28M0U | 60V 300mA MONOLITHIC DIODE ARRAY |

| 28M0DC | 60V 300mA MONOLITHIC DIODE ARRAY |

| 28M0DS | 60V 300mA MONOLITHIC DIODE ARRAY |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| 28F640C3BC80 | 制造商: 功能描述: 制造商:undefined 功能描述: |

| 28F640J3C120 | 制造商: 功能描述: 制造商:undefined 功能描述: |

| 28F640J3C-120 | 制造商: 功能描述: 制造商:undefined 功能描述: |

| 28F640J3D75 | 制造商:Intel 功能描述: 制造商: 功能描述: 制造商:undefined 功能描述: |

| 28F640J5 | 制造商:INTEL 制造商全稱:Intel Corporation 功能描述:5 Volt Intel StrataFlash? Memory |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。