- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄379803 > CD1865 (Intel Corp.) Intelligent Eight-Channel Communications Controller PDF資料下載

參數(shù)資料

| 型號: | CD1865 |

| 廠商: | Intel Corp. |

| 英文描述: | Intelligent Eight-Channel Communications Controller |

| 中文描述: | 智能八通道通信控制器 |

| 文件頁數(shù): | 102/150頁 |

| 文件大小: | 871K |

| 代理商: | CD1865 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁當(dāng)前第102頁第103頁第104頁第105頁第106頁第107頁第108頁第109頁第110頁第111頁第112頁第113頁第114頁第115頁第116頁第117頁第118頁第119頁第120頁第121頁第122頁第123頁第124頁第125頁第126頁第127頁第128頁第129頁第130頁第131頁第132頁第133頁第134頁第135頁第136頁第137頁第138頁第139頁第140頁第141頁第142頁第143頁第144頁第145頁第146頁第147頁第148頁第149頁第150頁

CD1865

—

Intelligent Eight-Channel Communications Controller

102

Datasheet

Within any one CD1865, the three Match registers must have unique values. In multiple CD1865

designs where service acknowledgments are cascaded, all Match registers of the same type (for

example, Receive) must have the same value.

In designs using register-based service acknowledgments (RRAR, TRAR, and MRAR), the

addresses of these registers must be placed in the equivalent Match register so that contains $77.

9.2.2.6

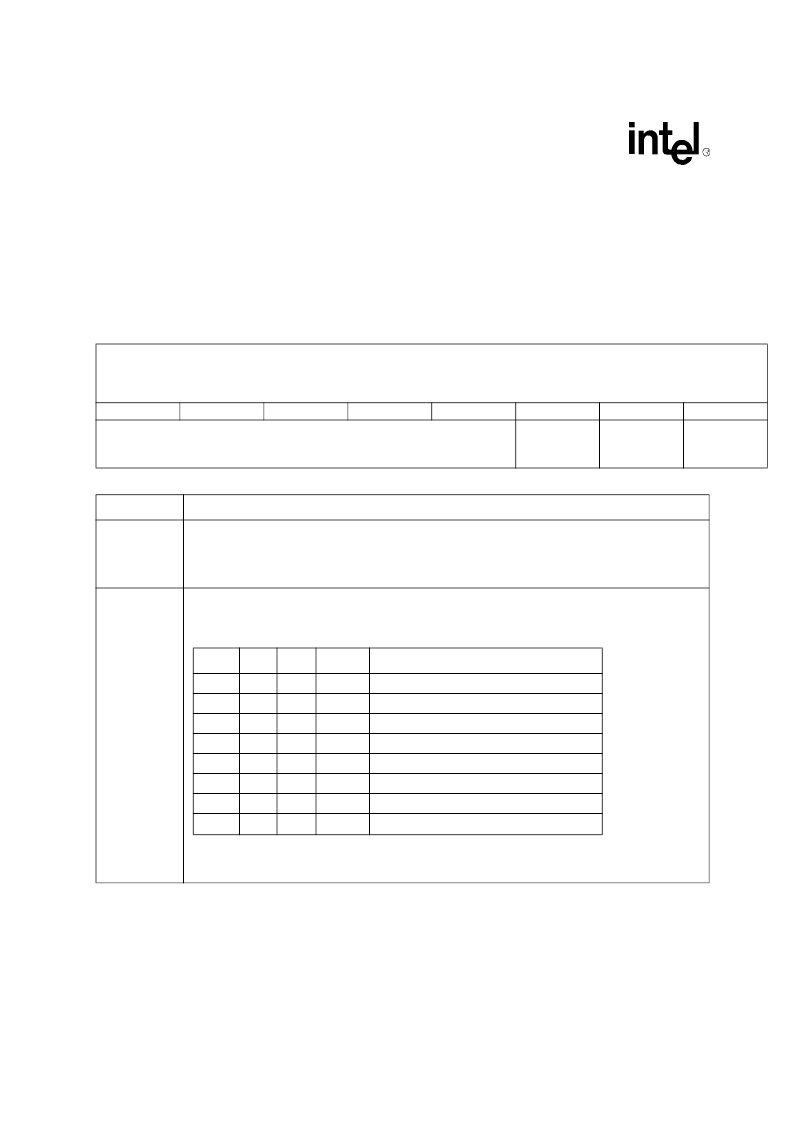

Global Vector Register

Register Name:

Register Description: Global Service Vector Register

Default Value: FF

Access: Read/Write

Bit 7

Bit 6

8-Bit Hex Address: $40

Intel Hex Address: $80

Motorola Hex Address: $81

Bit 5

Bit 4

Bit 3

Bit 2

Bit 1

Bit 0

Binary Value

IT2

IT1

IT0

Bit

Description

Bits 7:3

These bits are user-defined. However, in a multiple-device design, these five bits must have a unique value in

each CD1865 to identify which CD1865 is returning a vector during service acknowledgments. When writing

to this register, write eight bits at once; the CD1865 modifies the low-three bits automatically. Note that if this

register is read in a normal manner, the original eight bits are read and the modified bits from the last

acknowledgment cycle is not preserved.

Bits 2:0

These three bits indicate the group/type of service request occurring. These bit are supplied by the CD1865

during an acknowledgment cycle.

NOTE:

* This code is returned by the CD1865 only when RegAckEn is set, and DaisyEn is not set. In this

condition, the CD1865 must provide a vector when acknowledged. If the CD1865 receives an

acknowledgment for which it does not have a request pending, it returns

‘

000

’

.

IT2

IT1

IT0

Value

Group/Type

0

0

0

0

No Request Pending*

0

0

1

1

Modem Signal Change Service Request

0

1

0

2

Transmit Data Service Request

0

1

1

3

Receive Good Data Service Request

1

0

0

4

Reserved

1

0

1

5

Reserved

1

1

0

6

Reserved

1

1

1

7

Receive Exception Service Request

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| CD22100 | CMOS 4 x 4 Crosspoint Switch with Control Memory High-Voltage Type (20V Rating) |

| CD22100E | CMOS 4 x 4 Crosspoint Switch with Control Memory High-Voltage Type (20V Rating) |

| CD22100F | CMOS 4 x 4 Crosspoint Switch with Control Memory High-Voltage Type (20V Rating) |

| CD22101 | CMOS 4 x 4 x 2 Crosspoint Switch with Control Memory |

| CD22101E | CMOS 4 x 4 x 2 Crosspoint Switch with Control Memory |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| CD1865N | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Analog IC |

| CD1865P | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Analog IC |

| CD1866N | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Analog IC |

| CD1866P | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Analog IC |

| CD1867N | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Analog IC |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。