- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄98023 > ML60852A (LAPIS SEMICONDUCTOR CO LTD) UNIVERSAL SERIAL BUS CONTROLLER, PQFP44 PDF資料下載

參數(shù)資料

| 型號: | ML60852A |

| 廠商: | LAPIS SEMICONDUCTOR CO LTD |

| 元件分類: | 總線控制器 |

| 英文描述: | UNIVERSAL SERIAL BUS CONTROLLER, PQFP44 |

| 封裝: | PLASTIC, QFP-44 |

| 文件頁數(shù): | 60/82頁 |

| 文件大小: | 370K |

| 代理商: | ML60852A |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁當(dāng)前第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁

FEDL60852A-03

1Semiconductor

ML60852A

62/81

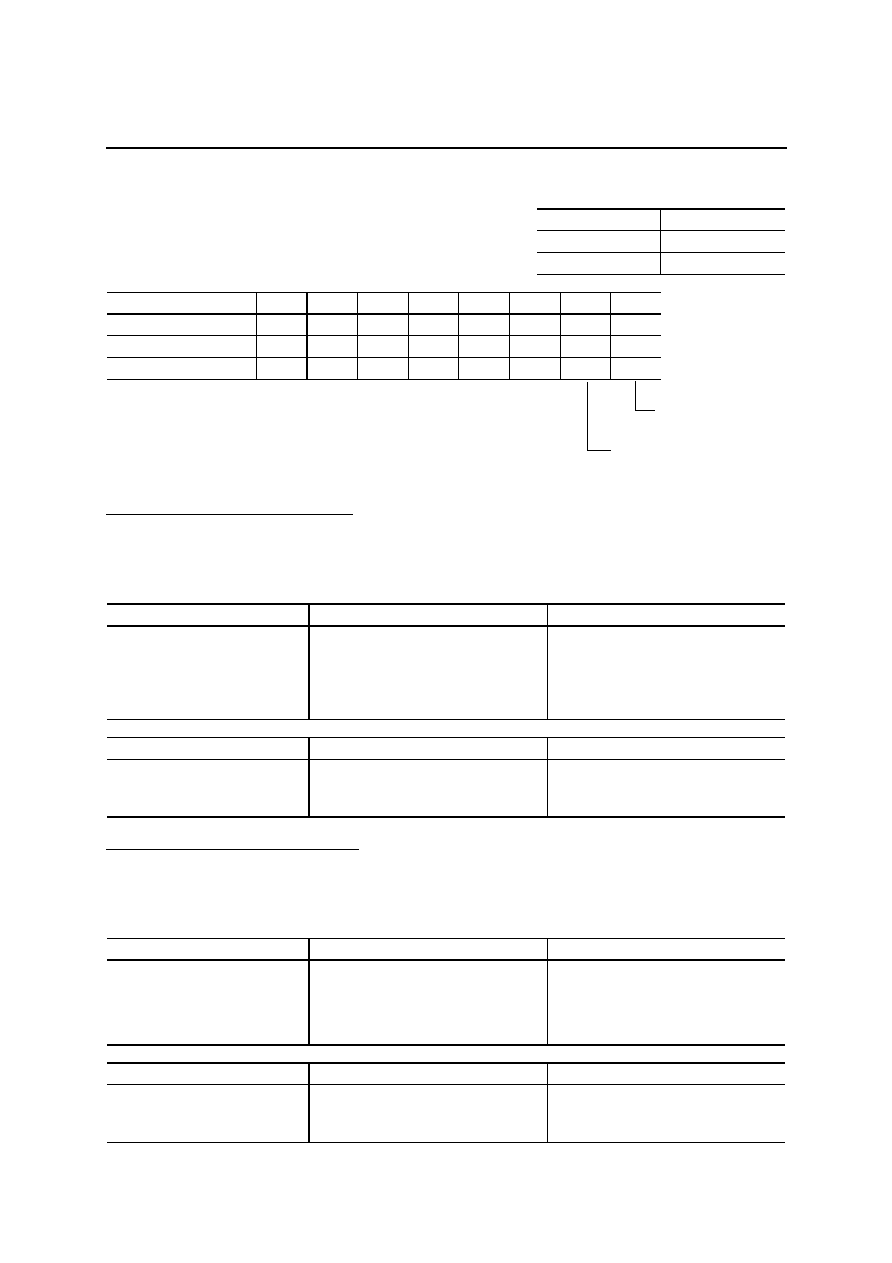

EP1, 2, 4, 5 Status Registers (EP1, 2, 4, 5STAT)

Address

0 x 61, 62, 64, 65

Type

Bit map

Access type

See below

D7

D6

D5

D4

D3

D2

D1

D0

After a hardware reset

0

0000

00

After a bus reset

0

0000

00

Definition

00

0000

This register is valid only when the corresponding EP has been set for bulk or interrupt transfer.

EP1,2,4,5 Receive packet ready bit (D0): This bit can be read by the local MCU. Also, this bit can be made “0” by

writing a “1” into bit D0. The asserting and de-asserting conditions of

this bit are as given below. The FIFOs of EP1, EP2, EP4, and EP5 have

a 2-layer structure and also there are independent packet ready bits for

layer A and layer B. The switching between these two layers is done

automatically by the ML60852A.

Bit name

Asserting condition

Operation when asserted

EPn Receive packet ready (D0)

When an error-free packet is received

in either layer A or layer B.

The local MCU can read the EP1

Receive FIFO. EP1 is locked in the

condition in which data packets have

been received by both layer A and

layer B.

Bit name

De-asserting condition

Operation when de-asserted

EPn Receive packet ready (D0)

When the local MCU has reset

(written a “1” in) the bits of both layer

A and layer B.

Reception can be made by EP1 when

the bit of either layer A or layer B has

been reset.

EP1,2,4,5 Transmit packet ready bit (D1): This bit can be read by the local MCU. Also, this bit can be made “1” by

writing a “1” into bit D1. The asserting and de-asserting conditions of

this bit are as given below. The FIFO of EP1 has a 2-layer structure and

also there are independent packet ready bits for layer A and layer B. The

switching between these two layers is done automatically by the

ML60852A.

Bit name

Asserting condition

Operation when asserted

EPn Transmit packet ready (D1) (1)When the local MCU has set the

bits of both layer A and layer B.

(2)When the local MCU has set the

bits of either layer A or layer B.

Transmission can be made from EP1

when either layer A or layer B has

been asserted.

Bit name

De-asserting condition

Operation when de-asserted

EPn Transmit packet ready (D1) When an ACK message is received

from the host for the data transmission

to either layer A or layer B.

EP1 is locked when transmit data has

not been prepared for both layer A

and layer B.

EP Receive packet

ready (Read/Reset)

EP Transmit packet ready

(Read/Set)

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| ML63187-XXXGA | 4-BIT, MROM, 2 MHz, MICROCONTROLLER, PQFP128 |

| ML63193-XXXWA | 4-BIT, MROM, 2 MHz, MICROCONTROLLER, UUC128 |

| ML64168-XXX | 4-BIT, MROM, 0.7 MHz, MICROCONTROLLER, UUC80 |

| ML64P168-NGP | 4-BIT, OTPROM, 0.7 MHz, MICROCONTROLLER, PQFP80 |

| ML64P168-NGA | 4-BIT, OTPROM, 0.7 MHz, MICROCONTROLLER, PQFP80 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| ML60852ATBZ010 | 功能描述:USB 接口集成電路 12 Mbps; USB Device Controller RoHS:否 制造商:Cypress Semiconductor 產(chǎn)品:USB 2.0 數(shù)據(jù)速率: 接口類型:SPI 工作電源電壓:3.15 V to 3.45 V 工作電源電流: 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:WLCSP-20 |

| ML60852ATBZ03A | 制造商:ROHM Semiconductor 功能描述: |

| ML-60-V2/80721 | 制造商:Thomas & Betts 功能描述: |

| ML61 | 制造商:MINILOGIC 制造商全稱:MINILOGIC 功能描述:Series Positive Voltage Detector |

| ML61_09 | 制造商:MINILOGIC 制造商全稱:MINILOGIC 功能描述:Positive Voltage Detector CMOS Low Power Consumption : Typical 1.0uA at Vin=2.0V |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。