- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄384021 > TMS320F28335_1 (Texas Instruments, Inc.) Variable Capacitance Diode for TV Tuner VHF Tuning; Ratings VR (V): 32; Characteristics n: 12.0 min; Characteristics rs (ohm) max: 0.85; Characteristics C (pF) max: C2 = 32.2 to 37.5 C25 = 2.57 to 3.0; Characteristics CVR/CVR: 2/25; Cl: 2.777; Package: UFP PDF資料下載

參數(shù)資料

| 型號: | TMS320F28335_1 |

| 廠商: | Texas Instruments, Inc. |

| 英文描述: | Variable Capacitance Diode for TV Tuner VHF Tuning; Ratings VR (V): 32; Characteristics n: 12.0 min; Characteristics rs (ohm) max: 0.85; Characteristics C (pF) max: C2 = 32.2 to 37.5 C25 = 2.57 to 3.0; Characteristics CVR/CVR: 2/25; Cl: 2.777; Package: UFP |

| 中文描述: | 數(shù)字信號控制器(DSC) |

| 文件頁數(shù): | 145/166頁 |

| 文件大?。?/td> | 1889K |

| 代理商: | TMS320F28335_1 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁第107頁第108頁第109頁第110頁第111頁第112頁第113頁第114頁第115頁第116頁第117頁第118頁第119頁第120頁第121頁第122頁第123頁第124頁第125頁第126頁第127頁第128頁第129頁第130頁第131頁第132頁第133頁第134頁第135頁第136頁第137頁第138頁第139頁第140頁第141頁第142頁第143頁第144頁當(dāng)前第145頁第146頁第147頁第148頁第149頁第150頁第151頁第152頁第153頁第154頁第155頁第156頁第157頁第158頁第159頁第160頁第161頁第162頁第163頁第164頁第165頁第166頁

www.ti.com

A

TMS320F28335, TMS320F28334, TMS320F28332

Digital Signal Controllers (DSCs)

SPRS439B–JUNE 2007–REVISED OCTOBER 2007

6.10.7.8

External Interface Ready-on-Write Timing With One External Wait State

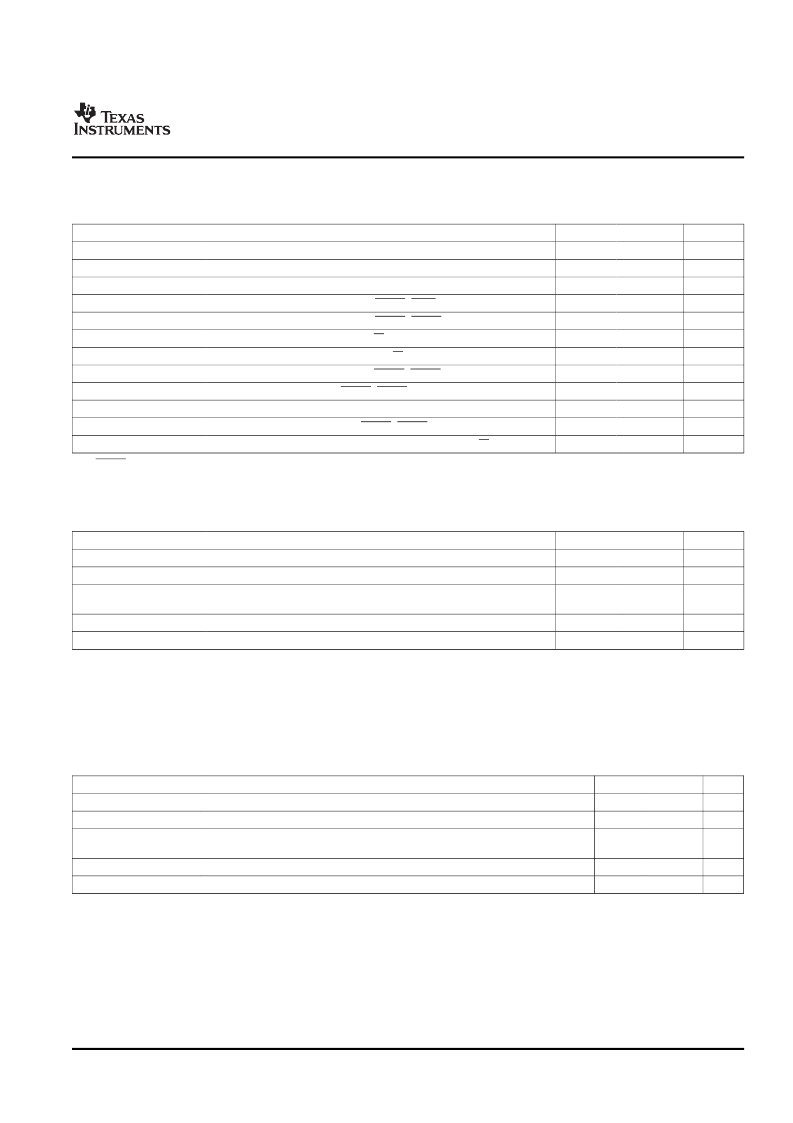

Table 6-46. External Interface Write Switching Characteristics (Ready-on-Write, 1 Wait State)

PARAMETER

Delay time, XCLKOUT high to zone chip-select active low

Delay time, XCLKOUT high or low to zone chip-select inactive high

Delay time, XCLKOUT high to address valid

Delay time, XCLKOUT high/low to XWE0, XWE1 low

(1)

Delay time, XCLKOUT high/low to XWE0, XWE1 high

(1)

Delay time, XCLKOUT high to XR/W low

Delay time, XCLKOUT high/low to XR/W high

Enable time, data bus driven from XWE0, XWE1 low

(1)

Delay time, data valid after XWE0, XWE1 active low

(1)

Hold time, address valid after zone chip-select inactive high

Hold time, write data valid after XWE0, XWE1 inactive high

(1)

Maximum time for DSP to release the data bus after XR/W inactive high

MIN

MAX

UNIT

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

t

d(XCOH-XZCSL)

t

d(XCOHL-XZCSH)

t

d(XCOH-XA)

t

d(XCOHL-XWEL)

t

d(XCOHL-XWEH)

t

d(XCOH-XRNWL)

t

d(XCOHL-XRNWH)

t

en(XD)XWEL

t

d(XWEL-XD)

t

h(XA)XZCSH

t

h(XD)XWE

t

dis(XD)XRNW

1

3

2

2

2

1

1

– 2

– 2

0

4

(2)

TW-2

(3)

4

(1)

(2)

(3)

XWE1 is used in 32-bit data bus mode only. In 16-bit, this signal is XA0.

During inactive cycles, the XINTF address bus always holds the last address put out on the bus. This includes alignment cycles.

TW = trail period, write access (see

Table 6-37

)

Table 6-47. Synchronous XREADY Timing Requirements (Ready-on-Write, 1 Wait State)

(1)

MIN

15

12

MAX

UNIT

ns

ns

ns

t

su(XRDYsynchL)XCOHL

t

h(XRDYsynchL)

t

e(XRDYsynchH)

Setup time, XREADY (synchronous) low before XCLKOUT high/low

Hold time, XREADY (synchronous) low

Earliest time XREADY (synchronous) can go high before the sampling

XCLKOUT edge

Setup time, XREADY (synchronous) high before XCLKOUT high/low

Hold time, XREADY (synchronous) held high after zone chip select high

3

t

su(XRDYsynchH)XCOHL

t

h(XRDYsynchH)XZCSH

15

0

ns

ns

(1)

The first XREADY (synchronous) sample occurs with respect to E in

Figure 6-27

:

E =(XWRLEAD + XWRACTIVE) t

When first sampled, if XREADY (synchronous) is high, then the access will complete. If XREADY (synchronous) is low, it is sampled

again each t

until it is high.

For each sample, setup time from the beginning of the access can be calculated as:

F = (XWRLEAD + XWRACTIVE +n –1) t

– t

where n is the sample number: n = 1, 2, 3, and so forth.

Table 6-48. Asynchronous XREADY Timing Requirements (Ready-on-Write, 1 Wait State)

(1)

MIN

11

MAX

UNIT

ns

ns

ns

t

su(XRDYasynchL)XCOHL

t

h(XRDYasynchL)

t

e(XRDYasynchH)

Setup time, XREADY (asynchronous) low before XCLKOUT high/low

Hold time, XREADY (asynchronous) low

Earliest time XREADY (asynchronous) can go high before the sampling

XCLKOUT edge

Setup time, XREADY (asynchronous) high before XCLKOUT high/low

Hold time, XREADY (asynchronous) held high after zone chip select high

8

3

t

su(XRDYasynchH)XCOHL

t

h(XRDYasynchH)XZCSH

11

0

ns

ns

(1)

The first XREADY (synchronous) sample occurs with respect to E in

Figure 6-27

:

E = (XWRLEAD + XWRACTIVE –2) t

. When first sampled, if XREADY (asynchronous) is high, then the access will complete. If

XREADY (asynchronous) is low, it is sampled again each t

until it is high.

For each sample, setup time from the beginning of the access can be calculated as:

F = (XWRLEAD + XWRACTIVE –3 + n) t

– t

where n is the sample number: n = 1, 2, 3, and so forth.

Submit Documentation Feedback

Electrical Specifications

145

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| TMS4024 | 9 X 64 DIGITAL STORAGE BUFFER (FIFO) |

| TMS4024JC | 9 X 64 DIGITAL STORAGE BUFFER (FIFO) |

| TMS4024NC | 9 X 64 DIGITAL STORAGE BUFFER (FIFO) |

| TMS4256-15SDE | 262,144-BIT DYNAMIC RANDOM-ACCESS MEMORIES |

| TMS4257-15SDE | 262,144-BIT DYNAMIC RANDOM-ACCESS MEMORIES |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| TMS320F28335PGFA | 功能描述:數(shù)字信號處理器和控制器 - DSP, DSC Digital Signal Controller RoHS:否 制造商:Microchip Technology 核心:dsPIC 數(shù)據(jù)總線寬度:16 bit 程序存儲器大小:16 KB 數(shù)據(jù) RAM 大小:2 KB 最大時鐘頻率:40 MHz 可編程輸入/輸出端數(shù)量:35 定時器數(shù)量:3 設(shè)備每秒兆指令數(shù):50 MIPs 工作電源電壓:3.3 V 最大工作溫度:+ 85 C 封裝 / 箱體:TQFP-44 安裝風(fēng)格:SMD/SMT |

| TMS320F28335PGFA | 制造商:Texas Instruments 功能描述:IC DSC 32BIT 512KB 150MHZ 1.995V LQFP176 |

| TMS320F28335PTPQ | 功能描述:數(shù)字信號處理器和控制器 - DSP, DSC Delfino Micrcntrlr RoHS:否 制造商:Microchip Technology 核心:dsPIC 數(shù)據(jù)總線寬度:16 bit 程序存儲器大小:16 KB 數(shù)據(jù) RAM 大小:2 KB 最大時鐘頻率:40 MHz 可編程輸入/輸出端數(shù)量:35 定時器數(shù)量:3 設(shè)備每秒兆指令數(shù):50 MIPs 工作電源電壓:3.3 V 最大工作溫度:+ 85 C 封裝 / 箱體:TQFP-44 安裝風(fēng)格:SMD/SMT |

| TMS320F28335PTPS | 功能描述:數(shù)字信號處理器和控制器 - DSP, DSC Delfino Micrcntrlr RoHS:否 制造商:Microchip Technology 核心:dsPIC 數(shù)據(jù)總線寬度:16 bit 程序存儲器大小:16 KB 數(shù)據(jù) RAM 大小:2 KB 最大時鐘頻率:40 MHz 可編程輸入/輸出端數(shù)量:35 定時器數(shù)量:3 設(shè)備每秒兆指令數(shù):50 MIPs 工作電源電壓:3.3 V 最大工作溫度:+ 85 C 封裝 / 箱體:TQFP-44 安裝風(fēng)格:SMD/SMT |

| TMS320F28335ZHHA | 功能描述:數(shù)字信號處理器和控制器 - DSP, DSC Digital Signal Controller RoHS:否 制造商:Microchip Technology 核心:dsPIC 數(shù)據(jù)總線寬度:16 bit 程序存儲器大小:16 KB 數(shù)據(jù) RAM 大小:2 KB 最大時鐘頻率:40 MHz 可編程輸入/輸出端數(shù)量:35 定時器數(shù)量:3 設(shè)備每秒兆指令數(shù):50 MIPs 工作電源電壓:3.3 V 最大工作溫度:+ 85 C 封裝 / 箱體:TQFP-44 安裝風(fēng)格:SMD/SMT |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。