- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄383723 > OR3LP26B Field-Programmable System Chip (FPSC) Embedded Master/Target PCI Interface PDF資料下載

參數(shù)資料

| 型號: | OR3LP26B |

| 英文描述: | Field-Programmable System Chip (FPSC) Embedded Master/Target PCI Interface |

| 中文描述: | 現(xiàn)場可編程系統(tǒng)芯片(促進(jìn)文化基金)嵌入式主/目標(biāo)PCI接口 |

| 文件頁數(shù): | 100/184頁 |

| 文件大?。?/td> | 5590K |

| 代理商: | OR3LP26B |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁當(dāng)前第100頁第101頁第102頁第103頁第104頁第105頁第106頁第107頁第108頁第109頁第110頁第111頁第112頁第113頁第114頁第115頁第116頁第117頁第118頁第119頁第120頁第121頁第122頁第123頁第124頁第125頁第126頁第127頁第128頁第129頁第130頁第131頁第132頁第133頁第134頁第135頁第136頁第137頁第138頁第139頁第140頁第141頁第142頁第143頁第144頁第145頁第146頁第147頁第148頁第149頁第150頁第151頁第152頁第153頁第154頁第155頁第156頁第157頁第158頁第159頁第160頁第161頁第162頁第163頁第164頁第165頁第166頁第167頁第168頁第169頁第170頁第171頁第172頁第173頁第174頁第175頁第176頁第177頁第178頁第179頁第180頁第181頁第182頁第183頁第184頁

ORCAOR3LP26B FPSC

Embedded Master/Target PCI Interface

Data Sheet

March 2000

100

L Lucent Technologies Inc.

PCI Bus Core Detailed Description

Quad Port

(continued)

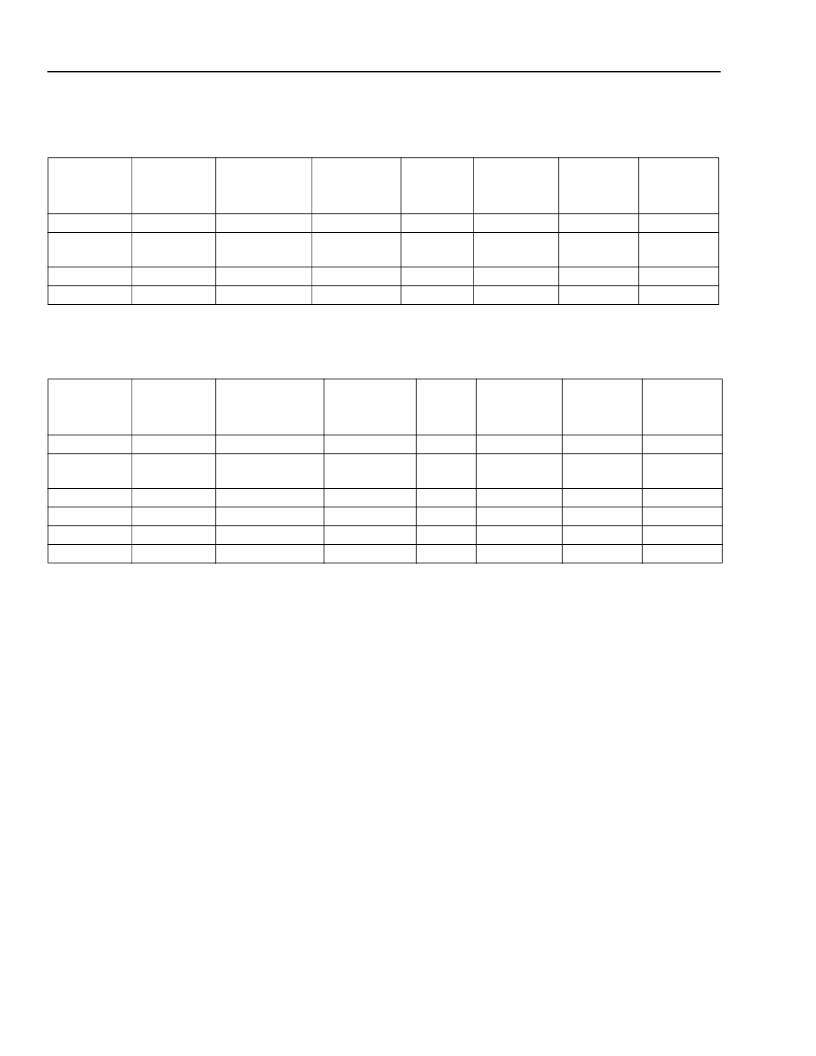

Table 37. Quad-Port Master Read, Duplicate Burst Length and 16-Bit Address

*

mrlastcycn

is 0 on the last data DWORD transfer.

Table 38. Quad-Port Master Read, Specified Burst Length and 64-Bit Address

*

mrlastcycn

is 0 on the last data DWORD transfer.

mstatecntr

Next State

of

mstatecntr

0

4

Description

Bus

maenn

mwlastcycn mrlastcycn mrdataenn

0

0

Idle

—

1

0

1

0

1

1

1

1

BE[7:0],

Address[15:0]

Data[31:0]

Data[63:32]

mwdata[35:0]

4

5

5 or 0

4 or 0

mrdata[31:0]

mrdata[31:0]

1

1

1

1

1

0*

0

0

mstatecntr

Next State

of

mstatecntr

0

1 or 4

Description

Bus

maenn

mwlastcycn mrlastcycn mrdataenn

0

0

Idle

—

1

0

1

1

1

1

1

1

BE[7:0], Burst

Length

Address[31:0]

Address[63:32]

Data[31:0]

Data[63:32]

mwdata[35:0]

1

2

4

5

2 or 4

4

5 or 0

4 or 0

mwdata[31:0]

mwdata[31:0]

mrdata[31:0]

mrdata[31:0]

0

0

1

1

1

0

1

1

1

1

1

0*

1

1

0

0

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| OR3TP12-6BA256 | Single 2.3V 10 MHz OP w/ CS, I temp, -40C to +85C, 8-TSSOP, T/R |

| OR3TP12-6BA256I | Single 2.3V 10 MHZ OP, -40C to +125C, 14-SOIC 150mil, TUBE |

| OR3TP12-6BA352 | Quad 2.3V 10 MHz OP, I temp, -40C to +85C, 14-PDIP, TUBE |

| OR3TP12-6BA352I | Quad 2.3V 10 MHz OP, I temp, -40C to +85C, 14-TSSOP, TUBE |

| OR3TP12-6PS240 | Single 2.3V 10 MHZ OP, -40C to +125C, 14-SOIC 150mil, T/R |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| OR3LP26BBA352-DB | 功能描述:FPGA - 現(xiàn)場可編程門陣列 FPSC PCI INTERFACE RoHS:否 制造商:Altera Corporation 系列:Cyclone V E 柵極數(shù)量: 邏輯塊數(shù)量:943 內(nèi)嵌式塊RAM - EBR:1956 kbit 輸入/輸出端數(shù)量:128 最大工作頻率:800 MHz 工作電源電壓:1.1 V 最大工作溫度:+ 70 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:FBGA-256 |

| OR3LP26BBM680-DB | 功能描述:FPGA - 現(xiàn)場可編程門陣列 FPSC PCI INTERFACE RoHS:否 制造商:Altera Corporation 系列:Cyclone V E 柵極數(shù)量: 邏輯塊數(shù)量:943 內(nèi)嵌式塊RAM - EBR:1956 kbit 輸入/輸出端數(shù)量:128 最大工作頻率:800 MHz 工作電源電壓:1.1 V 最大工作溫度:+ 70 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:FBGA-256 |

| OR3T125 | 制造商:AGERE 制造商全稱:AGERE 功能描述:3C and 3T Field-Programmable Gate Arrays |

| OR3T125-4BC432I | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Field Programmable Gate Array (FPGA) |

| OR3T125-4BC600I | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Field Programmable Gate Array (FPGA) |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。