- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄383723 > OR3TP12-6BA352I Quad 2.3V 10 MHz OP, I temp, -40C to +85C, 14-TSSOP, TUBE PDF資料下載

參數(shù)資料

| 型號(hào): | OR3TP12-6BA352I |

| 英文描述: | Quad 2.3V 10 MHz OP, I temp, -40C to +85C, 14-TSSOP, TUBE |

| 中文描述: | 用戶(hù)可編程ASIC的特殊功能 |

| 文件頁(yè)數(shù): | 1/128頁(yè) |

| 文件大小: | 2450K |

| 代理商: | OR3TP12-6BA352I |

當(dāng)前第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)第69頁(yè)第70頁(yè)第71頁(yè)第72頁(yè)第73頁(yè)第74頁(yè)第75頁(yè)第76頁(yè)第77頁(yè)第78頁(yè)第79頁(yè)第80頁(yè)第81頁(yè)第82頁(yè)第83頁(yè)第84頁(yè)第85頁(yè)第86頁(yè)第87頁(yè)第88頁(yè)第89頁(yè)第90頁(yè)第91頁(yè)第92頁(yè)第93頁(yè)第94頁(yè)第95頁(yè)第96頁(yè)第97頁(yè)第98頁(yè)第99頁(yè)第100頁(yè)第101頁(yè)第102頁(yè)第103頁(yè)第104頁(yè)第105頁(yè)第106頁(yè)第107頁(yè)第108頁(yè)第109頁(yè)第110頁(yè)第111頁(yè)第112頁(yè)第113頁(yè)第114頁(yè)第115頁(yè)第116頁(yè)第117頁(yè)第118頁(yè)第119頁(yè)第120頁(yè)第121頁(yè)第122頁(yè)第123頁(yè)第124頁(yè)第125頁(yè)第126頁(yè)第127頁(yè)第128頁(yè)

Data Sheet

March 2000

ORCA

OR3TP12 Field-Programmable System Chip (FPSC)

Embedded Master/Target PCI Interface

Introduction

Lucent Technologies Microelectronics Group has

developed a solution for designers who need the

many advantages of an FPGA-based design imple-

mentation coupled with the high bandwidth of the

industry-standard PCI interface. The ORCA

OR3TP12 FPSC provides a full-featured

33/50/66 MHz, 32-/64-bit PCI interface, fully

designed and tested, in hardware, plus FPGA logic

for user-programmable functions.

PCI Local Bus

PCI local bus, or simply, PCI bus, has become an

industry-standard interface protocol for use in appli-

cations ranging from desktop PC busing to high-

bandwidth backplanes in networking and communi-

cations equipment. The PCI bus specification* pro-

vides for both 5 V and 3.3 V signaling environments.

The PCI interface clock speed is specified in the

range from dc to 66 MHz with detailed specifications

at 33 MHz and 66 MHz as well as recommendations

for 50 MHz operation. Data paths are defined as

either 32-bit or 64-bit. These data path and frequency

combinations allow for the peak data transfer rates

described in Table 1.

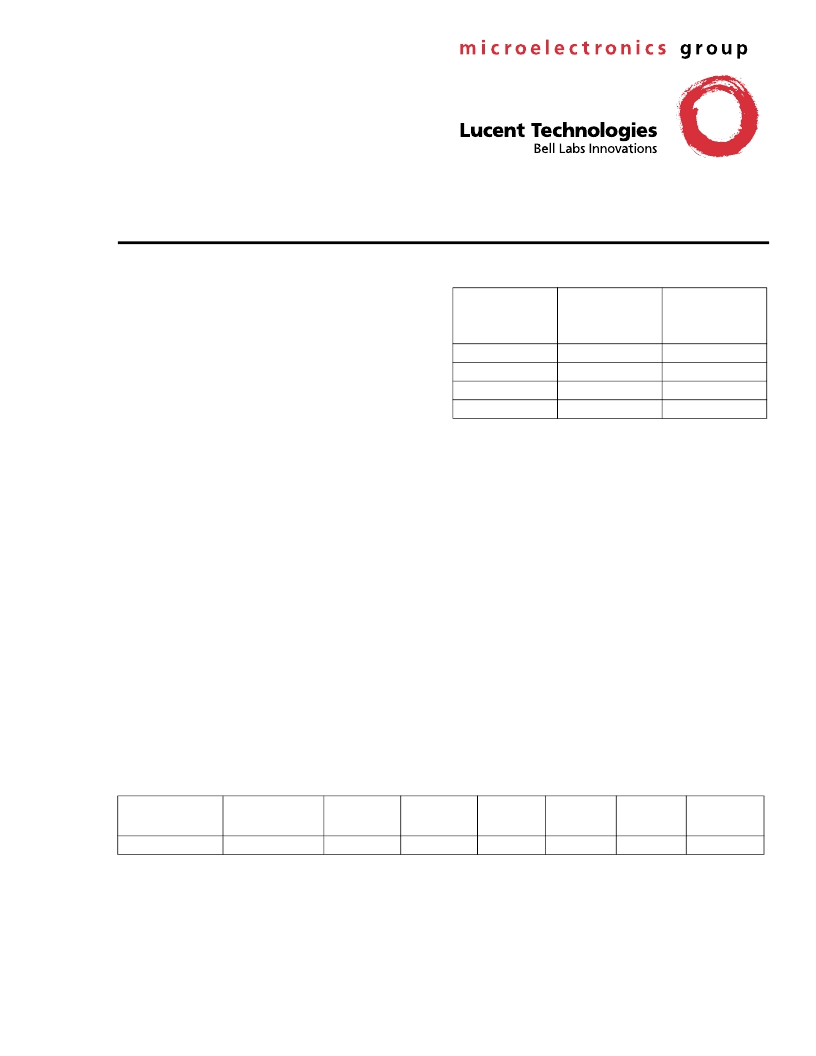

Table 1. PCI Local Bus Data Rates

The PCI bus is electrically specified so that no glue

logic is required to interface to the bus—PCI devices

interface directly to the PCI bus. Other features

include registers for device and subsystem identifica-

tion and autoconfiguration, support for 64-bit

addressing, and multimaster capability that allows

any PCI bus Master access to any PCI bus Target.

PCI Bus Core Highlights

I

Implemented in an ORCA Series 3 base array, dis-

placing the bottom four rows of 18 columns.

I

Core is a well-tested ASIC model.

I

Fully compliant to Revision 2.1 of PCI Local Bus

Specification (and designed for Revision 2.2).

* PCI Local Bus Specification Rev. 2.1, PCI SIG, June 1, 1995.

Clock

Frequency

(MHz)

33

33

66

66

Data Path

Width (bits)

Peak Data Rate

(Mbytes)

32

64

32

64

132

264

264

528

Table 2. ORCA PCI FPSC Solutions—Available FPGA Resources

* The embedded core and interface comprise approximately 85K standard-cell ASIC gates in addition to these usable gates. The usable

gate counts range from a logic-only gate count to a gate count assuming 30% of the PFUs/SLICs being used as RAMs. The logic-only

gate count includes each PFU/SLIC (counted as 108 gates per PFU/SLIC), including 12 gates per LUT/FF pair (eight per PFU), and 12

gates per SLIC/FF pair (one per PFU). Each of the four PIOs per PIC is counted as 16 gates (two FFs, fast-capture latch, output logic,

clk

drivers, and I/O buffers). PFUs used as RAM are counted at four gates per bit, with each PFU capable of implementing a 32

×

4 RAM (or

512 gates) per PFU.

Device

Usable Gates

*

Number of

LUTs

2016

Number of

Registers

2636

Max User

RAM

32K

Max User

I/Os

187

Array

Size

14

×

18

Number of

PFUs

252

OR3TP12

30K—60K

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| OR3TP12-6PS240 | Single 2.3V 10 MHZ OP, -40C to +125C, 14-SOIC 150mil, T/R |

| OR3TP12-6PS240I | Quad 2.3V 10 MHz OP, I temp, -40C to +85C, 14-SOIC 150mil, T/R |

| OR3TP12 | Field-Programmable System Chip (FPSC) Embedded Master/Target PCI Interface |

| OR62 | OR62 is a 6-input OR gate with 2x drive strength |

| OR73 | 7-input OR gate with 3x drive strength. |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| OR3TP126BAN256-DB | 制造商:Lattice Semiconductor Corporation 功能描述: |

| OR3TP12-6PS240 | 制造商:未知廠家 制造商全稱(chēng):未知廠家 功能描述:User Programmable Special Function ASIC |

| OR3TP12-6PS240I | 制造商:未知廠家 制造商全稱(chēng):未知廠家 功能描述:User Programmable Special Function ASIC |

| OR3TP127BA256-DB | 功能描述:FPGA - 現(xiàn)場(chǎng)可編程門(mén)陣列 2016 LUT 187 I/O RoHS:否 制造商:Altera Corporation 系列:Cyclone V E 柵極數(shù)量: 邏輯塊數(shù)量:943 內(nèi)嵌式塊RAM - EBR:1956 kbit 輸入/輸出端數(shù)量:128 最大工作頻率:800 MHz 工作電源電壓:1.1 V 最大工作溫度:+ 70 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:FBGA-256 |

| OR3TP127BA352-DB | 功能描述:FPGA - 現(xiàn)場(chǎng)可編程門(mén)陣列 2016 LUT 187 I/O RoHS:否 制造商:Altera Corporation 系列:Cyclone V E 柵極數(shù)量: 邏輯塊數(shù)量:943 內(nèi)嵌式塊RAM - EBR:1956 kbit 輸入/輸出端數(shù)量:128 最大工作頻率:800 MHz 工作電源電壓:1.1 V 最大工作溫度:+ 70 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:FBGA-256 |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。