- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄384756 > MT49H32M9C (Micron Technology, Inc.) 288Mb SIO REDUCED LATENCY(RLDRAM II) PDF資料下載

參數(shù)資料

| 型號: | MT49H32M9C |

| 廠商: | Micron Technology, Inc. |

| 英文描述: | 288Mb SIO REDUCED LATENCY(RLDRAM II) |

| 中文描述: | 288Mb二氧化硅約化延遲(延遲DRAM二) |

| 文件頁數(shù): | 31/44頁 |

| 文件大小: | 1117K |

| 代理商: | MT49H32M9C |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁當(dāng)前第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁

16 MEG x 18, 32 MEG x 9

2.5V V

EXT

, 1.8V V

DD

, HSTL, SIO, RLDRAM II

pdf: 09005aef80a41b59/zip: 09005aef811ba111

MT49H8M18C_2.fm - Rev. F 11/04 EN

Micron Technology, Inc., reserves the right to change products or specifications without notice.

2004 Micron Technology, Inc. All rights reserved.

31

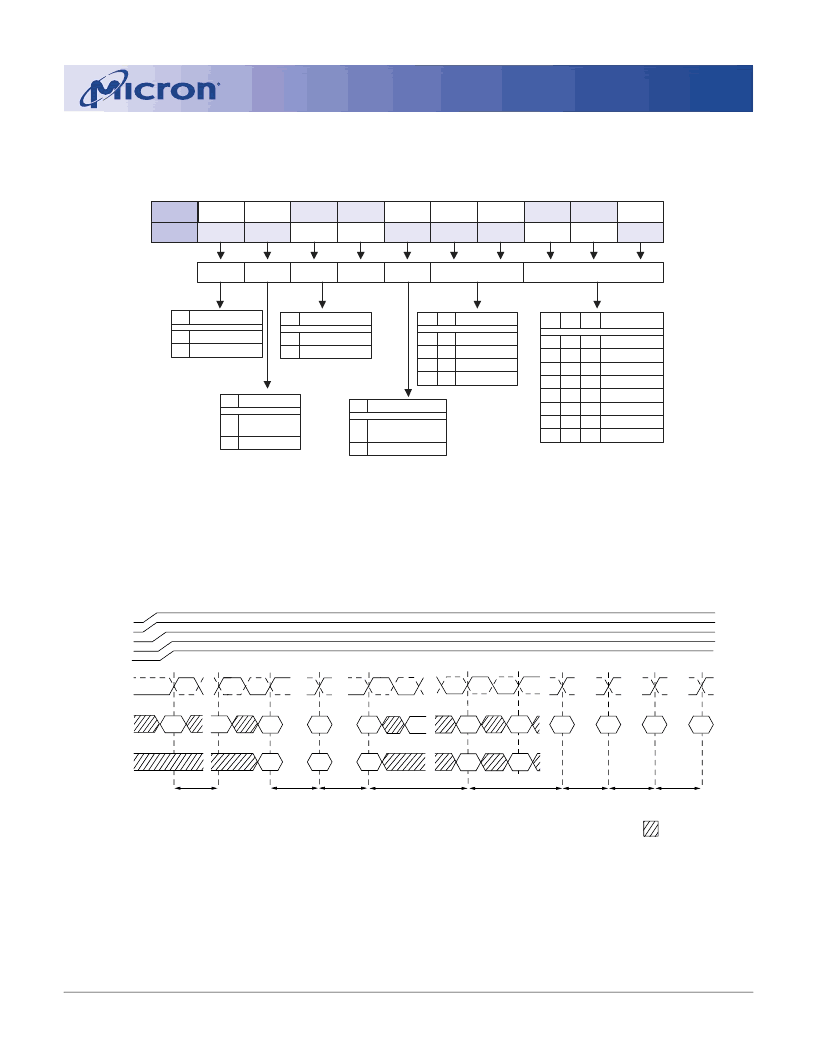

Figure 33: Mode Register Set Command in Multiplexed Address Mode

The addresses A0, A3, A4, A5, A8, and A9 must be set as follows in order to activate the mode register in the

multiplexed address mode.

NOTE:

1. Bits A(17:10)

must

be set to zero.

2. BL = 8 is not available for configuration 1.

3. ±15% temperature variation.

Figure 34: Power-Up Sequence in Multiplexed Address Mode

The following sequence must be respected in order to power up the RLDRAM in the multiplexed address mode.

NOTE:

1. Address A5 must be set HIGH (muxed address mode setting when RLDRAM is in normal mode of operation).

2. Address A5 must be set HIGH (muxed address mode setting when RLDRAM is already in muxed address mode).

A4

A5

A4

A3

A3

A0

A8

A9

A3x

0

1

BL

4

8

2

A4x

0

1

0

0

1

1

A9

A9y

0

1

A8

A4y A3y A0x

1

1

0

1

Configuration

Configuration

CoRLDRAM

1

2

(default)

1

2

2

reserved

reserved

reserved

not valid

2 (default)

DLL enabled

DLL Reset

DLL Reset

Burst Length

Burst Length

DLL Reset

Address

Mux

Address Mux

DLL reset (default)

3

reserved

1

1

0

1

0

1

0

0

1

0

0

0

1

1

0

0

1

0

1

0

Impedance

Matching

Impedance

Matching

A8x

0

1

Resistor

external

A5x

0

1

nonmultiplexed

(default)

address multiplexed

A9x

0

1

Enabled

Termination

Disabled (default)

On-Die

Termination

On-Die

Termination

Unused

Ax

Ay

internal 50

3

(default)

V

EXT

V

DD

V

DD

Q

V

REF

V

TT

CK#

CK

CMD

200μs MIN

t

MRSC

t

RC

2,048 cycles

MIN

6 × 2,048

cycles MIN

MRS

MRS

MRS

RF0

RF1

RF7

AC

DON’T CARE

ADD

A

1)

MRS

Ax

2)

Ay

t

MRSC

1 cycle

MIN

1 cycle

MIN

MRS: MRS command

RFx: REFRESH Bank x

AC: any command

NOP

NOP

NOP

NOP

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| MT49H32M9CFM-xx | 288Mb SIO REDUCED LATENCY(RLDRAM II) |

| MT4C1004J | 4 Meg x 1 FPM DRAM(4 M x 1快速頁面模式動態(tài)RAM) |

| MT4C4001STG-6 | standard or self refresh |

| MT4C4001STG-7 | standard or self refresh |

| MT4C4001STG-8 | standard or self refresh |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| MT49H32M9CFM-25 | 制造商:Micron Technology Inc 功能描述:DRAM CHIP RLDRAM 288MBIT 1.8V 144FBGA - Trays |

| MT49H32M9CFM-33 | 制造商:Micron Technology Inc 功能描述:DRAM CHIP RLDRAM 288MBIT 1.8V 144FBGA - Trays |

| MT49H32M9CFM-5 | 制造商:Micron Technology Inc 功能描述:DRAM CHIP RLDRAM 288MBIT 1.8V 144FBGA - Tape and Reel |

| MT49H32M9CFM-XX | 制造商:MICRON 制造商全稱:Micron Technology 功能描述:288Mb SIO REDUCED LATENCY(RLDRAM II) |

| MT49H32M9CHU-25 | 制造商:Micron Technology Inc 功能描述:DRAM CHIP RLDRAM 288MBIT 1.8V 144FBGA - Trays |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。