- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄296460 > MAX1359BCTL-T (MAXIM INTEGRATED PRODUCTS INC) SPECIALTY ANALOG CIRCUIT, QCC40 PDF資料下載

參數(shù)資料

| 型號(hào): | MAX1359BCTL-T |

| 廠商: | MAXIM INTEGRATED PRODUCTS INC |

| 元件分類: | 模擬信號(hào)調(diào)理 |

| 英文描述: | SPECIALTY ANALOG CIRCUIT, QCC40 |

| 封裝: | 6 X 6 MM, 0.80 MM HEIGHT, MO220, TQFN-40 |

| 文件頁數(shù): | 41/74頁 |

| 文件大?。?/td> | 1214K |

| 代理商: | MAX1359BCTL-T |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁當(dāng)前第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁

MAX1358/MAX1359/MAX1360

16-Bit Data-Acquisition Systems with ADC, DACs,

UPIOs, RTC, Voltage Monitors, and Temp Sensor

46

______________________________________________________________________________________

HFCE: High-frequency-clock enable bit. Set HFCE = 1

to enable the internal high-frequency clock source, and

set HFCE = 0 to disable the high-frequency clock

source.

If HFCE = 1 and CLKE = 1, the internal high-frequency

oscillator is enabled and is present at CLK. The power-

on default state is 1.

CKSEL<2:0>: Clock selection bits. These bits select

the FLL-based output clock frequency at the high-fre-

quency CLK pin as shown in Table 12. The power-on

default state is 001.

IO32E: Input/output 32kHz clock select bit. Set IO32E

= 0 to configure the CLK32K pin as an output and set

IO32E = 1 to configure the CLK32K pin as an input,

regardless of the signal on the 32KIN pin as shown in

Table 13.

External clock frequencies applied to CLK32K are

clock sources to the FLL, charge pump, and the signal-

detect comparator. The default power-on state is 0.

CK32E: CLK32K output-buffer enable bit. Set CK32E =

1 to enable the CLK32K output buffer as long as OSCE

= 1 and IO32E = 0, otherwise the CK32E bit will not be

asserted. Set CK32E = 0 to disable the CLK32K output

buffer. The power-on default state is 1.

CLKE: CLK output-buffer enable bit. Set CLKE = 1 to

enable the CLK output buffer. Set CLKE = 0 to disable

the buffer. Disabling the buffer is useful for saving

power in cases where the high-frequency clock is used

internally but is not needed externally. If HFCE = 0, or if

CLKE = 0, CLK remains low. The power-on default

state is 1.

INTP: Interrupt pin polarity bit. Set INTP = 1 to make

INT an active-high output when asserted and set INTP

= 0 to make INT an active-low output when asserted.

The power-on default state is 1.

WDE: Watchdog-enable bit. Set WDE = 1 to enable the

watchdog timer, which asserts

RESET low within 500ms

if the WATCHDOG register is not written. Set WDE = 0

to disable the watchdog timer. The power-on default

state is 0.

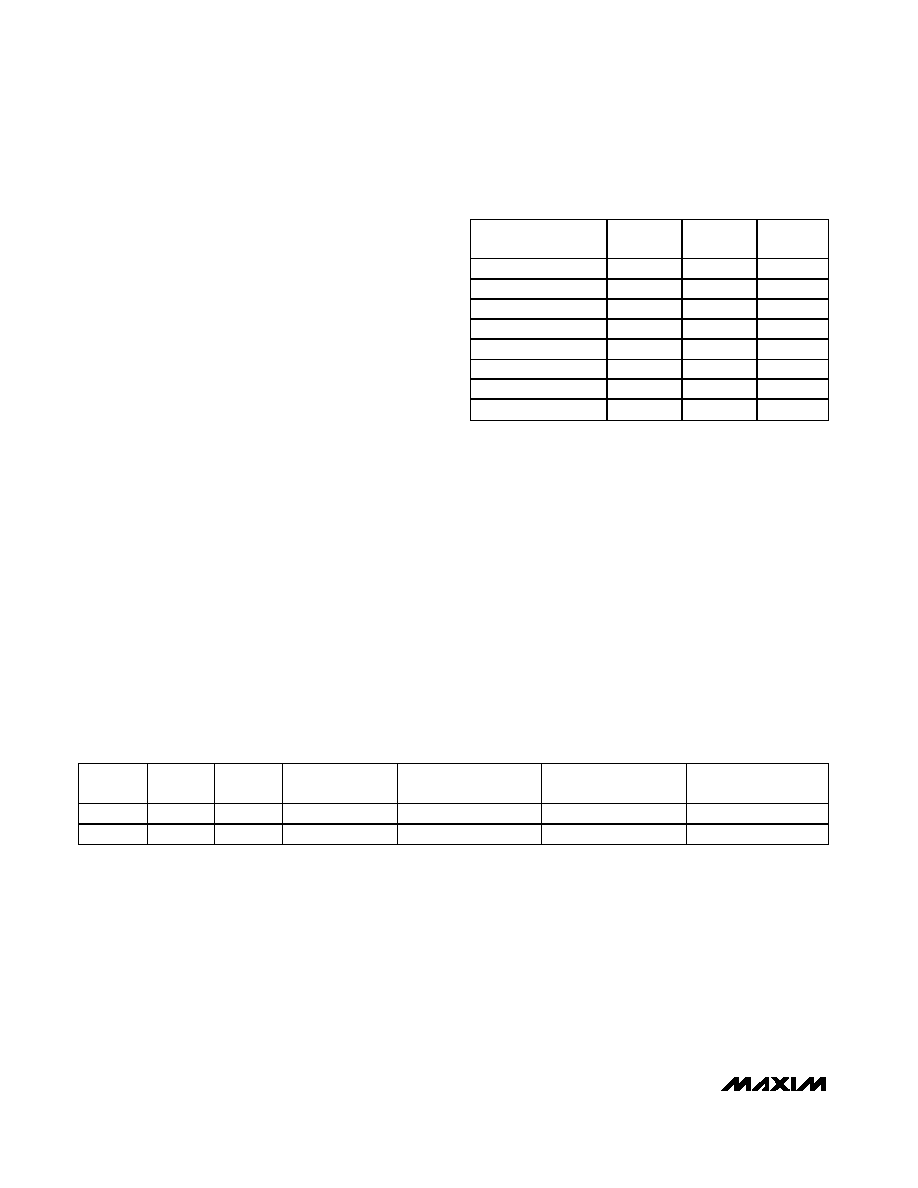

CLOCK FREQUENCY

(kHz)

CKSEL2

CKSEL1

CKSEL0

4915.2

0

2457.6

0

1

1228.8

0

1

0

614.4

0

1

32.768

1

0

16.384

1

0

1

8.192

1

0

4.096

1

Table 12. Setting the CLK Frequency

CLK32K

IO32E

32KIN, 32KOUT

RTC, PWM, WDT

CLOCK SOURCE

FLL, C/P, SDC INPUT

SOURCE

ADC CLOCK SOURCE

Output

10

XTAL attached

XTAL

FLL/HFCLK

Input

0

1

XTAL attached

XTAL

CLK32K

FLL/HFCLK

Table 13. Configuring the CLK32K as an Input or Output

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| MAX1359ACTL+ | SPECIALTY ANALOG CIRCUIT, QCC40 |

| MAX16005AUE+ | 6-CHANNEL POWER SUPPLY MANAGEMENT CKT, PDSO16 |

| MAX16005DUE+ | 6-CHANNEL POWER SUPPLY MANAGEMENT CKT, PDSO16 |

| MAX16072RS30D3+ | POWER SUPPLY SUPPORT CKT, PBGA4 |

| MAX17004AETJ+ | 3.3 A DUAL SWITCHING CONTROLLER, 575 kHz SWITCHING FREQ-MAX, QCC32 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| MAX1359BEGL | 制造商:Maxim Integrated Products 功能描述:- Rail/Tube |

| MAX1359BEGL-T | 制造商:Maxim Integrated Products 功能描述:- Tape and Reel |

| MAX1359BETL | 功能描述:數(shù)據(jù)轉(zhuǎn)換系統(tǒng) RoHS:否 制造商:Texas Instruments 轉(zhuǎn)換速率:0.001 MSPs 分辨率:24 bit 最大工作溫度:+ 125 C 最小工作溫度:- 40 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:TQFP-64 封裝:Reel |

| MAX1359BETL+ | 功能描述:數(shù)據(jù)轉(zhuǎn)換系統(tǒng) 16-Bit 2Ch .512ksps 3.6V Precision SoIC RoHS:否 制造商:Texas Instruments 轉(zhuǎn)換速率:0.001 MSPs 分辨率:24 bit 最大工作溫度:+ 125 C 最小工作溫度:- 40 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:TQFP-64 封裝:Reel |

| MAX1359BETL+T | 功能描述:數(shù)據(jù)轉(zhuǎn)換系統(tǒng) 16-Bit 2Ch .512ksps 3.6V Precision SoIC RoHS:否 制造商:Texas Instruments 轉(zhuǎn)換速率:0.001 MSPs 分辨率:24 bit 最大工作溫度:+ 125 C 最小工作溫度:- 40 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:TQFP-64 封裝:Reel |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。