- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄383876 > T7256A Compliance with the New ETSI PSD Requirement PDF資料下載

參數(shù)資料

| 型號: | T7256A |

| 英文描述: | Compliance with the New ETSI PSD Requirement |

| 中文描述: | 符合新的ETSI PSD的要求 |

| 文件頁數(shù): | 38/116頁 |

| 文件大小: | 1056K |

| 代理商: | T7256A |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁當(dāng)前第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁第107頁第108頁第109頁第110頁第111頁第112頁第113頁第114頁第115頁第116頁

Data Sheet

January 1998

T7256 Single-Chip NT1 (SCNT1) Transceiver

34

Lucent Technologies Inc.

Microprocessor Interface Description

(continued)

Registers

(continued)

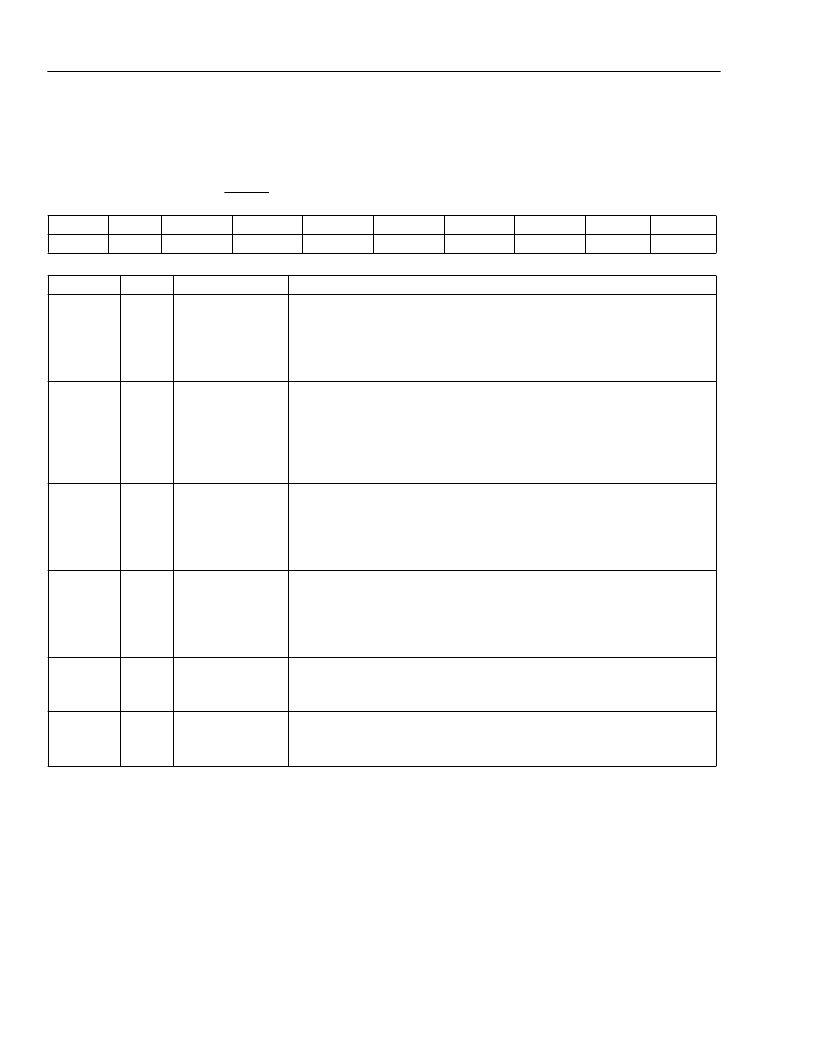

Table 19. U-Interface Interrupt Register (Address 13h)

These bits are cleared during RESET.

Reg

UIR0

R/W

R

Bit 7

—

Bit 6

—

Bit 5

TSFINT

Bit 4

RSFINT

Bit 3

OUSC

Bit 2

BERR

Bit 1

ACTSC

Bit 0

EOCSC

Register

UIR0

Bit

0

Symbol

EOCSC

Name/Description

eoc State Change on U-Interface.

Activates (set to 1) when the re-

ceived eoc message changes state. Bit is cleared on read. See eoc

State Machine Description section for details.

0—No change in eoc state.

1—eoc state change.

Activation/Deactivation State Change on U-Interface.

Activates (set

to 1) during changes in the status bits monitoring U-interface activation

and deactivation (ACTR and XACT, register CFR1, bits 0 and 1). Bit

cleared on read.

0—No activation/deactivation activity.

1—Change in state of activation/deactivation bits.

Block Error on U-Interface.

Activates (set to 1) when received signal

contains either a near-end (NEBE = 0) or a far-end (FEBE = 0) block er-

ror. Bit cleared on read.

0—No block errors.

1—Block error.

Other U-Interface State Change.

Activates (set to 1) when any of the

following bits change state: OOF, UOA, AIB, and Rx, y (all reserved U-

interface status bits). Bit cleared on read.

0—No state change.

1—State change.

Receive Superframe Interrupt.

Activates (set to 1) when the receive

superframe boundary occurs. Bit cleared on read.

0 to 1—First 2B+D data of the receive U superframe.

Transmit Superframe Interrupt.

Activates (set to 1) when the transmit

superframe boundary occurs. Bit cleared on read.

0 to 1—First 2B+D data of the transmit U superframe.

UIR0

1

ACTSC

UIR0

2

BERR

UIR0

3

OUSC

UIR0

4

RSFINT

UIR0

5

TSFINT

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| T7288 | CEPT/E1 Line Interface(CEPT/E1 線接口) |

| T7290A | DS1/T1/CEPT/E1 Line Interface(DS1/T1/CEPT/E1 線接口) |

| T7295-1 | E3 Integrated Line Receiver(E3 集成線接收器) |

| T7295-6 | DS3/SONET STS-1 Integrated Line Receiver(DS3/SONET STS-1 集成線接收器) |

| T7296 | Integrated Line Transmitter(集成PCM線傳送器) |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| T7257 | 制造商:TE Connectivity 功能描述: |

| T-726 | 制造商:RHOMBUS-IND 制造商全稱:Rhombus Industries Inc. 功能描述:ADSL Line Interface Transformers |

| T7263 | 制造商:TE Connectivity 功能描述: |

| T7263A | 制造商:Toshiba America Electronic Components 功能描述:T7263A |

| T7264 | 制造商:TE Connectivity 功能描述: |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。