- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄383838 > ST20GP6 MAX 7000 CPLD 256 MC 208-RQFP PDF資料下載

參數(shù)資料

| 型號(hào): | ST20GP6 |

| 英文描述: | MAX 7000 CPLD 256 MC 208-RQFP |

| 中文描述: | GPS處理器 |

| 文件頁數(shù): | 27/116頁 |

| 文件大?。?/td> | 1107K |

| 代理商: | ST20GP6 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁當(dāng)前第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁第107頁第108頁第109頁第110頁第111頁第112頁第113頁第114頁第115頁第116頁

ST20-GP1

27/116

4.6.4

Trap handlers and trapped processes can be set up and examined via the ldtraph, sttraph

ldtrapped and sttrapped instructions. Table 4.8 describes the instructions that may be used when

dealing with traps.

Trap instructions

The first four instructions transfer data to/from the trap handler structures or trapped process

structures from/to an area in memory. In these instructions

Areg

contains the trap group code (see

Table 4.4) and

Breg

points to the 4 word area of memory used as the source or destination of the

transfer. In addition

Creg

contains the priority of the handler to be installed/examined in the case of

ldtraph or sttraph. ldtrappedand sttrappedapply only to the current priority.

If the LoadTraptrap is enabled then ldtraphand ldtrappeddo not perform the transfer but set the

LoadTrap

trap flag. If the StoreTrap trap is enabled then sttraphand sttrappeddo not perform the

transfer but set the

StoreTrap

trap flag.

The trap enable masks are encoded by an array of bits (see Table 4.5) which are set to indicate

which traps are enabled. This array of bits is stored in the lower half-word of the

Enables

register.

There is an

Enables

register for each priority. Traps are enabled or disabled by loading a mask into

Areg

with bits set to indicate which traps are to be affected and the priority to affect in

Breg

.

Executing trapenbORs the mask supplied in

Areg

with the trap enables mask in the

Enables

register for the priority in

Breg

. Executing trapdisnegates the mask supplied in

Areg

and ANDs it

with the trap enables mask in the

Enables

register for the priority in

Breg

. Both instructions return

the previous value of the trap enables mask in

Areg

.

4.6.5

There are various restrictions that must be placed on trap handlers to ensure that they work

correctly.

1

Trap handlers must not deschedule or timeslice. Trap handlers alter the

Enables

masks,

therefore they must not allow other processes to execute until they have completed.

Restrictions on trap handlers

2

Trap handlers must have their

Enable

masks set to mask all traps in their trap group to

avoid the possibility of a trap handler trapping to itself.

Trap handlers must terminate via the tret (trap return) instruction. The only exception to this

is that a scheduler kernel may use restartto return to a previously shadowed process.

3

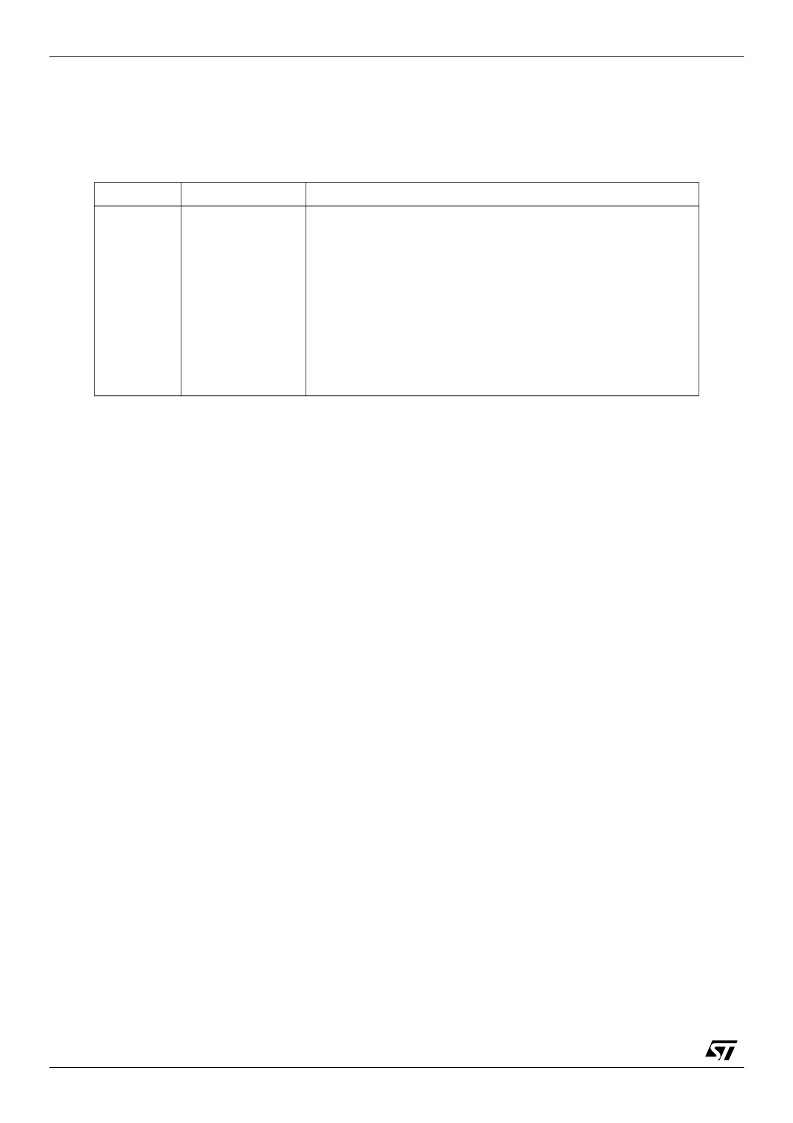

Instruction

Meaning

Use

ldtraph

load trap handler

load the trap handler from memory to the trap handler descriptor

sttraph

store trap handler

store an existing trap handler descriptor to memory

ldtrapped

load trapped

load replacement trapped process status from memory

sttrapped

store trapped

store trapped process status to memory

trapenb

trap enable

enable traps

trapdis

trap disable

disable traps

tret

trap return

used to return from a trap handler

causeerror

cause error

program can simulate the occurrence of an error

Table 4.7 Instructions which may be used when dealing with traps

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| ST25C02AB1 | IC FLEX 6000 FPGA 16K 144-TQFP |

| ST25C02AB6 | Stratix FPGA 25K FBGA-672 |

| ST25C02AM1 | IC ACEX 1K FPGA 100K 208-PQFP |

| ST25C02AM6 | Cyclone II FPGA 20K FBGA-256 |

| ST25C04ML1 | IC FLEX 6000 FPGA 24K 144-TQFP |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| ST20-GP6 | 制造商:STMICROELECTRONICS 制造商全稱:STMicroelectronics 功能描述:GPS PROCESSOR |

| ST20GP6CT33S | 制造商:STMICROELECTRONICS 制造商全稱:STMicroelectronics 功能描述:GPS PROCESSOR |

| ST20GP6CX33S | 功能描述:射頻無線雜項(xiàng) GPS Processor RoHS:否 制造商:Texas Instruments 工作頻率:112 kHz to 205 kHz 電源電壓-最大:3.6 V 電源電壓-最小:3 V 電源電流:8 mA 最大功率耗散: 工作溫度范圍:- 40 C to + 110 C 封裝 / 箱體:VQFN-48 封裝:Reel |

| ST20GP6CX33STR | 功能描述:射頻無線雜項(xiàng) GPS Processor RoHS:否 制造商:Texas Instruments 工作頻率:112 kHz to 205 kHz 電源電壓-最大:3.6 V 電源電壓-最小:3 V 電源電流:8 mA 最大功率耗散: 工作溫度范圍:- 40 C to + 110 C 封裝 / 箱體:VQFN-48 封裝:Reel |

| ST20GP6X33S | 制造商:STMICROELECTRONICS 制造商全稱:STMicroelectronics 功能描述:GPS PROCESSOR |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。