- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄180243 > M7A3PE600-FFGG484I FPGA, 600000 GATES, PBGA484 PDF資料下載

參數(shù)資料

| 型號(hào): | M7A3PE600-FFGG484I |

| 元件分類: | FPGA |

| 英文描述: | FPGA, 600000 GATES, PBGA484 |

| 封裝: | 1 MM PITCH, GREEN, FBGA-484 |

| 文件頁數(shù): | 137/168頁 |

| 文件大?。?/td> | 1335K |

| 代理商: | M7A3PE600-FFGG484I |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁第107頁第108頁第109頁第110頁第111頁第112頁第113頁第114頁第115頁第116頁第117頁第118頁第119頁第120頁第121頁第122頁第123頁第124頁第125頁第126頁第127頁第128頁第129頁第130頁第131頁第132頁第133頁第134頁第135頁第136頁當(dāng)前第137頁第138頁第139頁第140頁第141頁第142頁第143頁第144頁第145頁第146頁第147頁第148頁第149頁第150頁第151頁第152頁第153頁第154頁第155頁第156頁第157頁第158頁第159頁第160頁第161頁第162頁第163頁第164頁第165頁第166頁第167頁第168頁

ProASIC3E Flash Family FPGAs

3- 2

A dvanced v0. 5

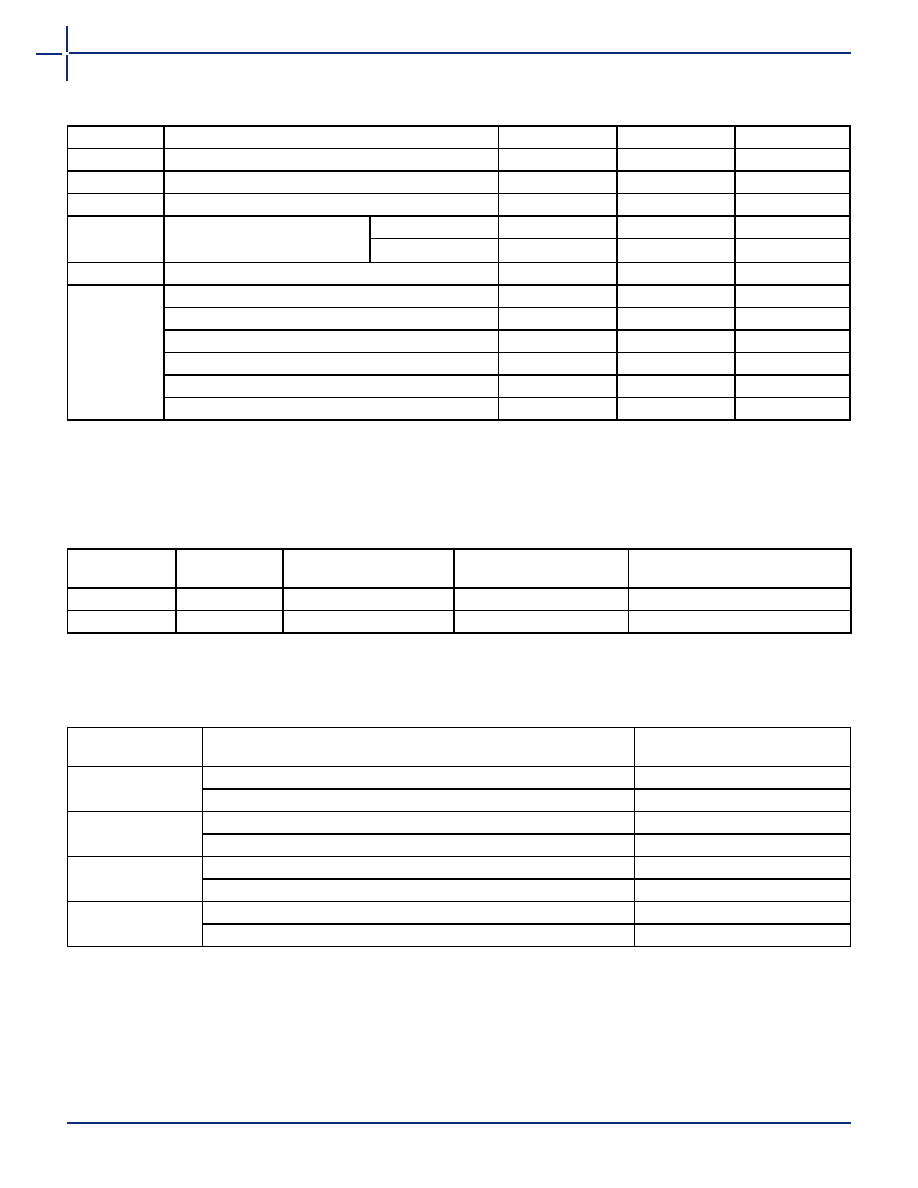

Table 3-2

Recommended Operating Conditions

Symbol

Parameter

Commercial

Industrial

Units

TA, TJ

Ambient and Junction temperature

0 to +70

–40 to +85

°C

VCC

1.5 V DC core supply voltage

1.425 to 1.575

V

VJTAG

JTAG DC voltage

1.4 to 3.6

V

VPUMP

Programming voltage

Programming Mode

3.0 to 3.6

V

Operation3

0 to 3.6

V

VCCPLL

Analog power supply (PLL)

1.4 to 1.6

V

VCCI and VMV 1.5 V DC supply voltage

1.425 to 1.575

V

1.8 V DC supply voltage

1.7 to 1.9

V

2.5 V DC supply voltage

2.3 to 2.7

V

3.3 V DC supply voltage

3.0 to 3.6

V

LVDS/BLVDS/M-LVDS differential I/O

2.375 to 2.625

V

LVPECL differential I/O

3.0 to 3.6

V

Notes:

1. The ranges given here are for power supplies only. The recommended input voltage ranges specific to each I/O standard are given

2. All parameters representing voltages are measured with respect to GND unless otherwise specified.

3. VPUMP can be left floating during normal operation (not programming mode).

Table 3-3 Flash Programming Limits - Retention, Storage and Operating Temperature1

Product Grade

Programming

Cycles

Program Retention

(Biased/Unbiased)

Maximum Storage

Temperature TSTG (°C)

2

Maximum Operating Junction

Temperature TJ (°C)

2

Commercial

500

20 years

110

Industrial

500

20 years

110

Notes:

1. This is a stress rating only, functional operation at any other condition other than those indicates is not implied.

2. These limits apply for program/data retention only. Refer to tables 3-1 and 3-2 for device operating conditions and absolute limits.

Table 3-4

Overshoot and Undershoot Limits (as measured on quiet I/Os)1

VCCI and VMV

Average VCCI-GND Overshoot or Undershoot Duration as a

Percentage of Clock Cycle2

Maximum Overshoot/

Undershoot)2

2.7 V or less

10%

1.4 V

5%

1.49 V

3 V

10%

1.1 V

5%

1.19 V

3.3 V

10%

0.79 V

5%

0.88 V

3.6 V

10%

0.45 V

5%

0.54 V

Notes:

1. Based on reliability requirements at 85°C.

2. The duration is allowed at one cycle out of six clock cycles (estimated SSO density over cycles). If the overshoot/undershoot occurs at

1 out of 2 cycles, then the maximum overshoot/undershoot has to be reduced by 0.15 V.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| M7A3PE600-FPQ208I | FPGA, 600000 GATES, PQFP208 |

| M7A3PE600-FPQG208I | FPGA, 600000 GATES, PQFP208 |

| M7R-R63FAJFREQ | CRYSTAL OSCILLATOR, CLOCK, 80.001 MHz - 125 MHz, CMOS/TTL OUTPUT |

| M7R-R68TAJFREQ | CRYSTAL OSCILLATOR, CLOCK, 80.001 MHz - 125 MHz, CMOS/TTL OUTPUT |

| M7R76FCJFREQ | CRYSTAL OSCILLATOR, CLOCK, 80.001 MHz - 125 MHz, CMOS OUTPUT |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| M7A5 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:MEDIUM CURRENT SILICON RECTIFIERS |

| M7A9 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:MEDIUM CURRENT SILICON RECTIFIERS |

| M7AFS600-1FG256 | 制造商:Microsemi Corporation 功能描述:FPGA FUSION 600K GATES 1282.05MHZ 130NM 1.5V 256FBGA - Trays 制造商:Microsemi SOC Products Group 功能描述:FPGA FUSION 600K GATES 1282.05MHZ 130NM 1.5V 256FBGA - Trays |

| M7AFS600-1FG256ES | 制造商:ACTEL 制造商全稱:Actel Corporation 功能描述:Actel Fusion Mixed-Signal FPGAs |

| M7AFS600-1FG256I | 制造商:Microsemi Corporation 功能描述:FPGA FUSION 600K GATES 1282.05MHZ 130NM 1.5V 256FBGA - Trays 制造商:Microsemi SOC Products Group 功能描述:FPGA FUSION 600K GATES 1282.05MHZ 130NM 1.5V 256FBGA - Trays |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。