- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄98083 > SME1430LGA-480 64-BIT, 480 MHz, RISC PROCESSOR, CBGA587 PDF資料下載

參數(shù)資料

| 型號: | SME1430LGA-480 |

| 元件分類: | 微控制器/微處理器 |

| 英文描述: | 64-BIT, 480 MHz, RISC PROCESSOR, CBGA587 |

| 封裝: | CERAMIC, LGA-587 |

| 文件頁數(shù): | 11/60頁 |

| 文件大?。?/td> | 646K |

| 代理商: | SME1430LGA-480 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁當(dāng)前第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁

19

Highly Integrated 64-Bit RISC; L2-Cache, DRAM, PCI Interfaces

UltraSPARC-IIi CPU

SME1430LGA-360

SME1430LGA-440

SME1430LGA-480

May 1999

Sun Microsystems, Inc

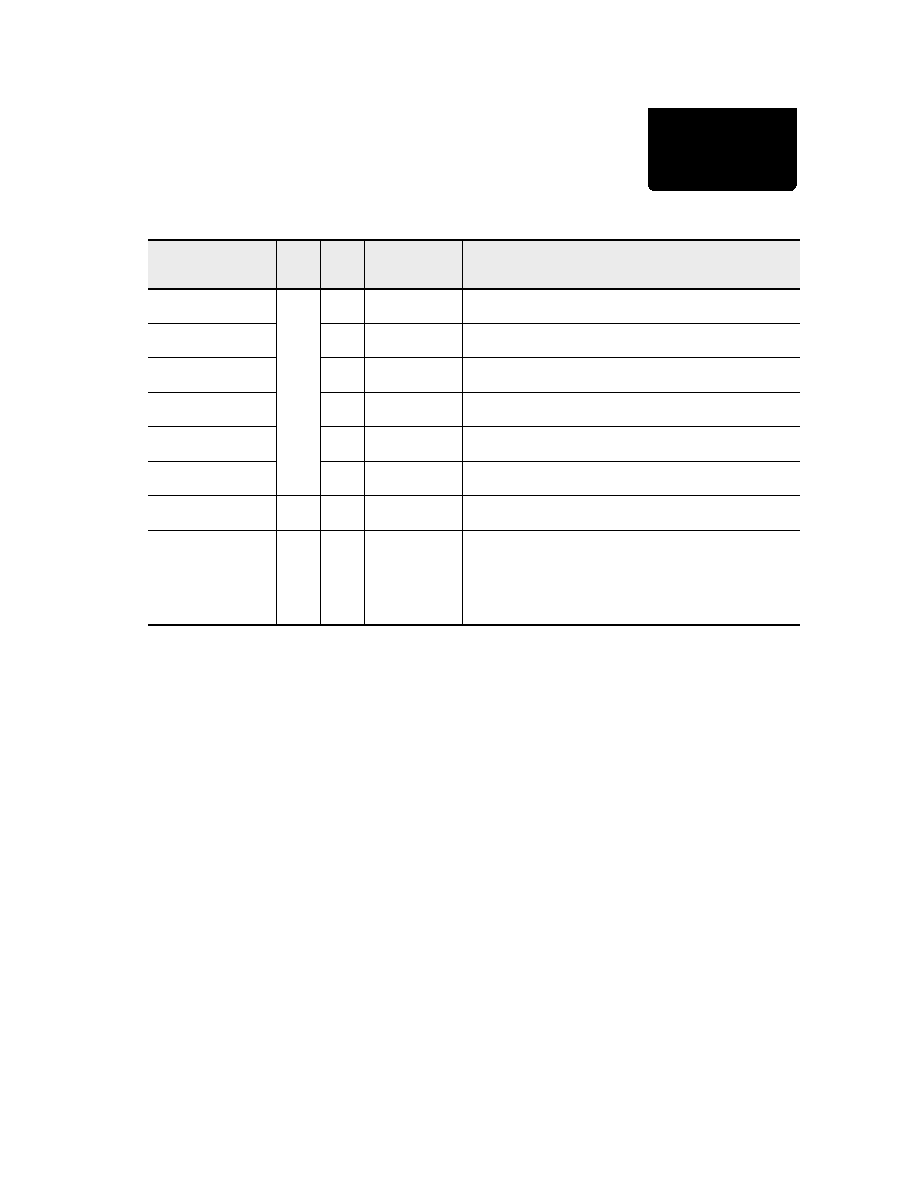

Initialization Interface

Symbol

Volts

Type

Signal

Transitions

Aligned with:

Name and Function

P_RESET_L

3.3 V

I

Not Aligned

For non power-on resets (debug); asynchronous assertion and

de-assertion; active low

X_RESET_L

I

Driven to signal XIR traps (debug); acts as non-maskable

interrupt; asynchronous assertion and de-assertion; active low

SYS_RESET_L

I

Driven for power-on resets (POR); asynchronous assertion and

de-assertion; active low [1]

1. SYS_RESET_L must be a clean indication that 3.3 V, 5 V, etc. are stable and within specication. No anomalies may be present, beginning when

the power supplies are turned on and extending until the signals are within specication. When signals are within specication, the power supply

can transition monotonically to 3.3 V.

RST_L

O

Resets PCI subsystem; Asynchronous assertion and monotonic

deassertion; also used for UPA64S reset

RMTV_SEL

I

Red Mode Trap Vector Select; pull up if alternate PC-compatible

boot vector is required

CLKSEL

I

Pullup to enable the 2x function of the CLKA/B PLL; L2-cache

interface still works at 1/2 the internal processor clock rate

EPD

1.9 V

O

Asserted when

the UltraSPARC-IIi CPU is in clock shutdown

mode; use P_RESET_L to re-start

SYNC_3TO1_MODE

3.3 V

I

This is a new pin denition for the SME1430 IIi CPU. (The

SME1040 IIi CPU denes this pin as VSSPLL.)

This pin selects the number of synchronizing stages between the

PCI interface and the CPU core clock domains. A 0 selects a two

stage synchronizer, a 1 selects three stages. This pin is normally

tied low as previously done when it was dened as VSSPLL

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| SME1701-BGA133 | 32-BIT, 133 MHz, MICROPROCESSOR, PBGA316 |

| SME5224AUPA-360 | 64-BIT, 360 MHz, RISC PROCESSOR |

| SME5410MCZ-270 | 64-BIT, 270 MHz, RISC PROCESSOR, XMA |

| SME5434PCI-440 | 64-BIT, 440 MHz, RISC PROCESSOR, XMA |

| SME5434PCI-480 | 64-BIT, 480 MHz, RISC PROCESSOR, XMA |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| SME14P95J4173 | 制造商:LIT 功能描述:Connector |

| SME160T1R0H | 制造商:Russell 功能描述: |

| SME160T221M22X40LL | 制造商:United Chemi-Con Inc 功能描述: |

| SME160T2R2H | 制造商:Russell 功能描述: |

| SME160VB10RM10X16FT | 制造商:United Chemi-Con Inc 功能描述: |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。