- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄360257 > 56F8014 (飛思卡爾半導(dǎo)體(中國(guó))有限公司) 16-bit Digital Signal Controllers PDF資料下載

參數(shù)資料

| 型號(hào): | 56F8014 |

| 廠商: | 飛思卡爾半導(dǎo)體(中國(guó))有限公司 |

| 英文描述: | 16-bit Digital Signal Controllers |

| 中文描述: | 16位數(shù)字信號(hào)控制器 |

| 文件頁(yè)數(shù): | 19/124頁(yè) |

| 文件大小: | 1878K |

| 代理商: | 56F8014 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)當(dāng)前第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)第69頁(yè)第70頁(yè)第71頁(yè)第72頁(yè)第73頁(yè)第74頁(yè)第75頁(yè)第76頁(yè)第77頁(yè)第78頁(yè)第79頁(yè)第80頁(yè)第81頁(yè)第82頁(yè)第83頁(yè)第84頁(yè)第85頁(yè)第86頁(yè)第87頁(yè)第88頁(yè)第89頁(yè)第90頁(yè)第91頁(yè)第92頁(yè)第93頁(yè)第94頁(yè)第95頁(yè)第96頁(yè)第97頁(yè)第98頁(yè)第99頁(yè)第100頁(yè)第101頁(yè)第102頁(yè)第103頁(yè)第104頁(yè)第105頁(yè)第106頁(yè)第107頁(yè)第108頁(yè)第109頁(yè)第110頁(yè)第111頁(yè)第112頁(yè)第113頁(yè)第114頁(yè)第115頁(yè)第116頁(yè)第117頁(yè)第118頁(yè)第119頁(yè)第120頁(yè)第121頁(yè)第122頁(yè)第123頁(yè)第124頁(yè)

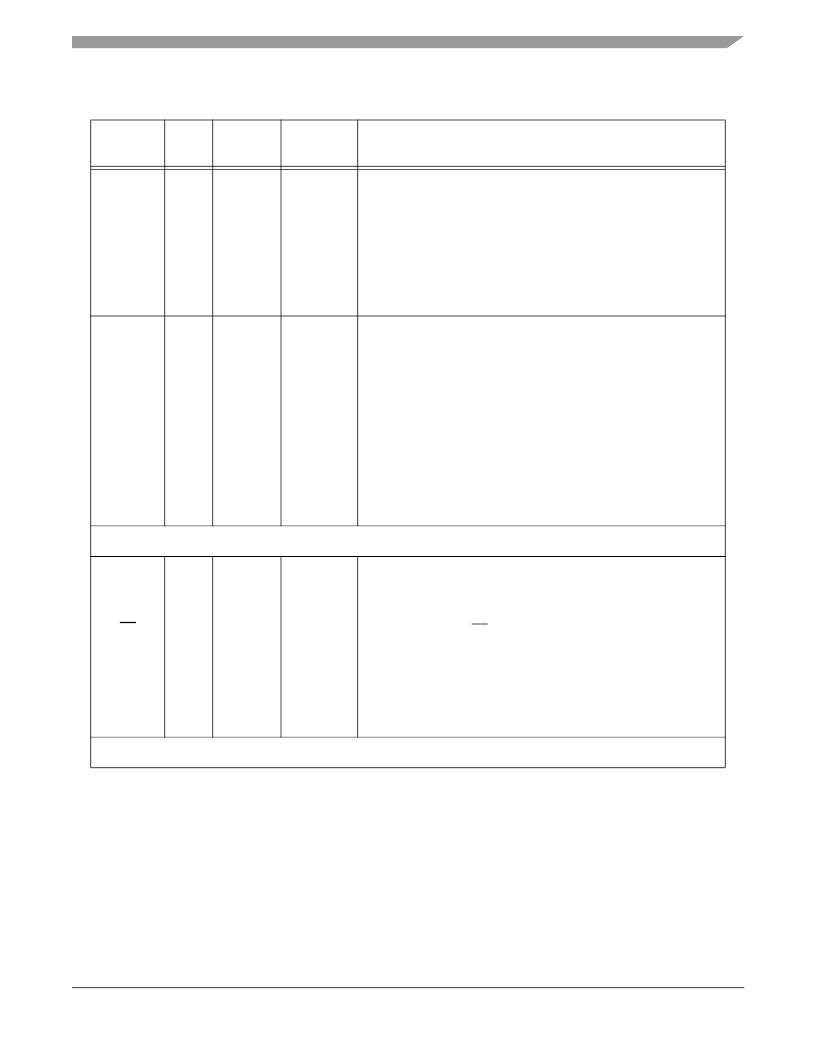

56F8014 Signal Pins

56F8014 Technical Data, Rev. 3

Freescale Semiconductor

Preliminary

19

TDO

(GPIOD1)

31

Output

Input/

Output

Tri-stated,

pulled high

internally

Test Data Output

— This tri-stateable output pin provides a serial

output data stream from the JTAG/EOnCE port. It is driven in the

shift-IR and shift-DR controller states, and changes on the falling

edge of TCK.

Port D GPIO

— This GPIO pin can be individually programmed as

an input or output pin.

After reset, the default state is TDO.

GPIOB0

(SCLK)

(SCL

3

)

21

Input/

Output

Input/

Output

Input/

Output

Input, pulled

high

internally

Port B GPIO

— This GPIO pin can be individually programmed as

an input or output pin.

SPI Serial Clock

— In the master mode, this pin serves as an

output, clocking slaved listeners. In slave mode, this pin serves as

the data clock input. A Schmitt trigger input is used for noise

immunity.

Serial Data

— This pin serves as the I

2

C serial clock.

After reset, the default state is GPIOB0. The peripheral functionality

is controlled via the SIM. See

Section 6.3.8

.

3.

This signal is also brought out on the GPIOB7 pin.

GPIOB1

(SS)

(SDA

4

)

1

Input/

Output

Input

Input/

Output

Input, pulled

high

internally

Port B GPIO

— This GPIO pin can be individually programmed as

an input or output pin.

SPI Slave Select

— SS is used in slave mode to indicate to the SPI

module that the current transfer is to be received.

Serial Clock

— This pin serves as the I

2

C serial data line.

After reset, the default state is GPIOB1. The peripheral functionality

is controlled via the SIM. See

Section 6.3.8

.

4.

This signal is also brought out on the GPIOB6 pin.

Return to

Table 2-2

Table 2-3 56F8014 Signal and Package Information for the 32-Pin LQFP (Continued)

Signal

Name

LQFP

Pin No.

Type

State During

Reset

Signal Description

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| 56F802 | 16-bit Digital Signal Controllers |

| 57037 | PNT MRKING LYT BLUE INK 1LTR |

| 5703AY | Single Digit LED Numeric Display |

| 5301AHR | Dual/Triple Ultra-Low-Voltage SOT23 µP Supervisory Circuits |

| 5301AP | Single Digit LED Numeric Display |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| 56F8014_07 | 制造商:FREESCALE 制造商全稱:Freescale Semiconductor, Inc 功能描述:16-bit Digital Signal Controllers |

| 56F8014_08 | 制造商:FREESCALE 制造商全稱:Freescale Semiconductor, Inc 功能描述:16-bit Digital Signal Controllers |

| 56F801E | 制造商:FREESCALE 制造商全稱:Freescale Semiconductor, Inc 功能描述:16-bit Digital Signal Controllers |

| 56F801XBLUG | 制造商:FREESCALE 制造商全稱:Freescale Semiconductor, Inc 功能描述:16-bit Digital Signal Controllers |

| 56F802 | 制造商:FREESCALE 制造商全稱:Freescale Semiconductor, Inc 功能描述:16-bit Digital Signal Controllers |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。