- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄360257 > 56F8014 (飛思卡爾半導(dǎo)體(中國)有限公司) 16-bit Digital Signal Controllers PDF資料下載

參數(shù)資料

| 型號: | 56F8014 |

| 廠商: | 飛思卡爾半導(dǎo)體(中國)有限公司 |

| 英文描述: | 16-bit Digital Signal Controllers |

| 中文描述: | 16位數(shù)字信號控制器 |

| 文件頁數(shù): | 107/124頁 |

| 文件大?。?/td> | 1878K |

| 代理商: | 56F8014 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁當(dāng)前第107頁第108頁第109頁第110頁第111頁第112頁第113頁第114頁第115頁第116頁第117頁第118頁第119頁第120頁第121頁第122頁第123頁第124頁

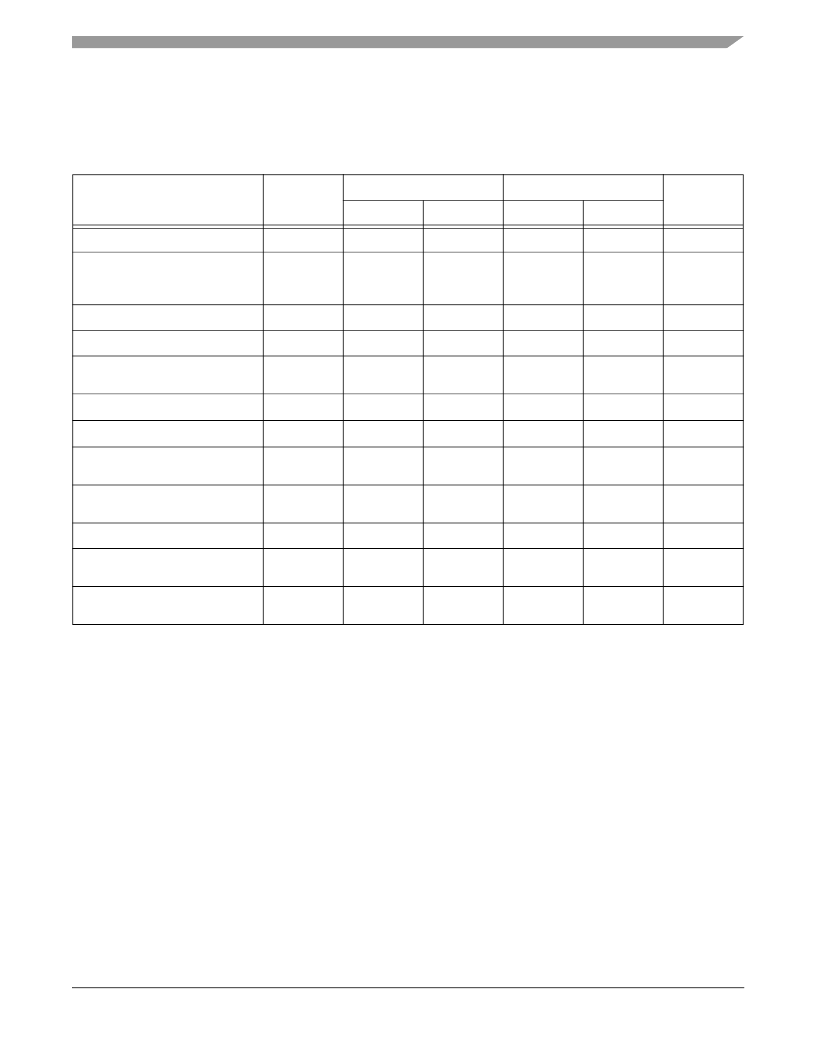

Inter-Integrated Circuit Interface (I2C) Timing

56F8014 Technical Data, Rev. 3

Freescale Semiconductor

Preliminary

107

10.12 Inter-Integrated Circuit Interface (I

2

C) Timing

Table 10-17 I

2

C Timing

Characteristic

Symbol

Standard Mode

Fast Mode

Unit

Minimum

Maximum

Minimum

Maximum

SCL Clock Frequency

f

SCL

0

100

0

400

kHz

Hold time (repeated ) START

condition. After this period, the

first clock pulse is generated.

t

HD; STA

4.0

0.6

μ

s

LOW period of the SCL clock

t

LOW

4.7

1.25

μ

s

HIGH period of the SCL clock

t

HIGH

4.0

0.6

μ

s

Set-up time for a repeated START

condition

t

SU; STA

4.7

0.6

μ

s

Data hold time for I

2

C bus devices

t

HD; DAT

0

1

1. A device must internally provide a hold time of at least 300ns for the SDA signal (referred to the V

IH

min of the SCL signal) to

bridge the undefined region of the falling edge of SCL.

2. The maximum t

HD;

DAT

has only to be met if the device does not stretch the LOW period (t

LOW

) of the SCL signal.

3. A Fast mode I

2

C bus device can be used in a Standard mode I

2

C bus system, but the requirement t

SU; DAT

> = 250ns must then

be met. This will automatically be the case if the device does not stretch the LOW period of the SCL signal. If such a device does

stretch the LOW period of the SCL signal, it must output the next data bit to the SDA line

t

rmax

+ t

SU; DAT

= 1000 + 250 = 1250ns (according to the Standard mode I

2

C bus specification) before the SCL line is released.

4. C

b

= total capacitance of the one bus line in pF.

3.45

2

0

1

0.9

2

μ

s

Data set-up time

t

SU; DAT

250

100

3

ns

Rise time of both SDA and SCL

signals

t

r

1000

2 +0.1C

b4

300

ns

Fall time of both SDA and SCL

signals

t

f

300

2 +0.1C

b4

300

ns

Set-up time for STOP condition

t

SU; STO

4.0

0.6

μ

s

Bus free time between STOP and

START condition

t

BUF

4.7

1.3

μ

s

Pulse width of spikes that must be

suppressed by the input filter

t

SP

N/A

N/A

0.0

50

ns

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| 56F802 | 16-bit Digital Signal Controllers |

| 57037 | PNT MRKING LYT BLUE INK 1LTR |

| 5703AY | Single Digit LED Numeric Display |

| 5301AHR | Dual/Triple Ultra-Low-Voltage SOT23 µP Supervisory Circuits |

| 5301AP | Single Digit LED Numeric Display |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| 56F8014_07 | 制造商:FREESCALE 制造商全稱:Freescale Semiconductor, Inc 功能描述:16-bit Digital Signal Controllers |

| 56F8014_08 | 制造商:FREESCALE 制造商全稱:Freescale Semiconductor, Inc 功能描述:16-bit Digital Signal Controllers |

| 56F801E | 制造商:FREESCALE 制造商全稱:Freescale Semiconductor, Inc 功能描述:16-bit Digital Signal Controllers |

| 56F801XBLUG | 制造商:FREESCALE 制造商全稱:Freescale Semiconductor, Inc 功能描述:16-bit Digital Signal Controllers |

| 56F802 | 制造商:FREESCALE 制造商全稱:Freescale Semiconductor, Inc 功能描述:16-bit Digital Signal Controllers |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。