- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄383804 > SCANPSC110FSC (FAIRCHILD SEMICONDUCTOR CORP) SCAN Bridge Hierarchical and Multidrop Addressable JTAG Port (IEEE1149.1 System Test Support) PDF資料下載

參數(shù)資料

| 型號: | SCANPSC110FSC |

| 廠商: | FAIRCHILD SEMICONDUCTOR CORP |

| 元件分類: | 微控制器/微處理器 |

| 英文描述: | SCAN Bridge Hierarchical and Multidrop Addressable JTAG Port (IEEE1149.1 System Test Support) |

| 中文描述: | SPECIALTY MICROPROCESSOR CIRCUIT, PDSO28 |

| 封裝: | 0.300 INCH, MS-013, SOIC-28 |

| 文件頁數(shù): | 14/25頁 |

| 文件大?。?/td> | 283K |

| 代理商: | SCANPSC110FSC |

www.fairchildsemi.com

14

S

Register Descriptions

(Continued)

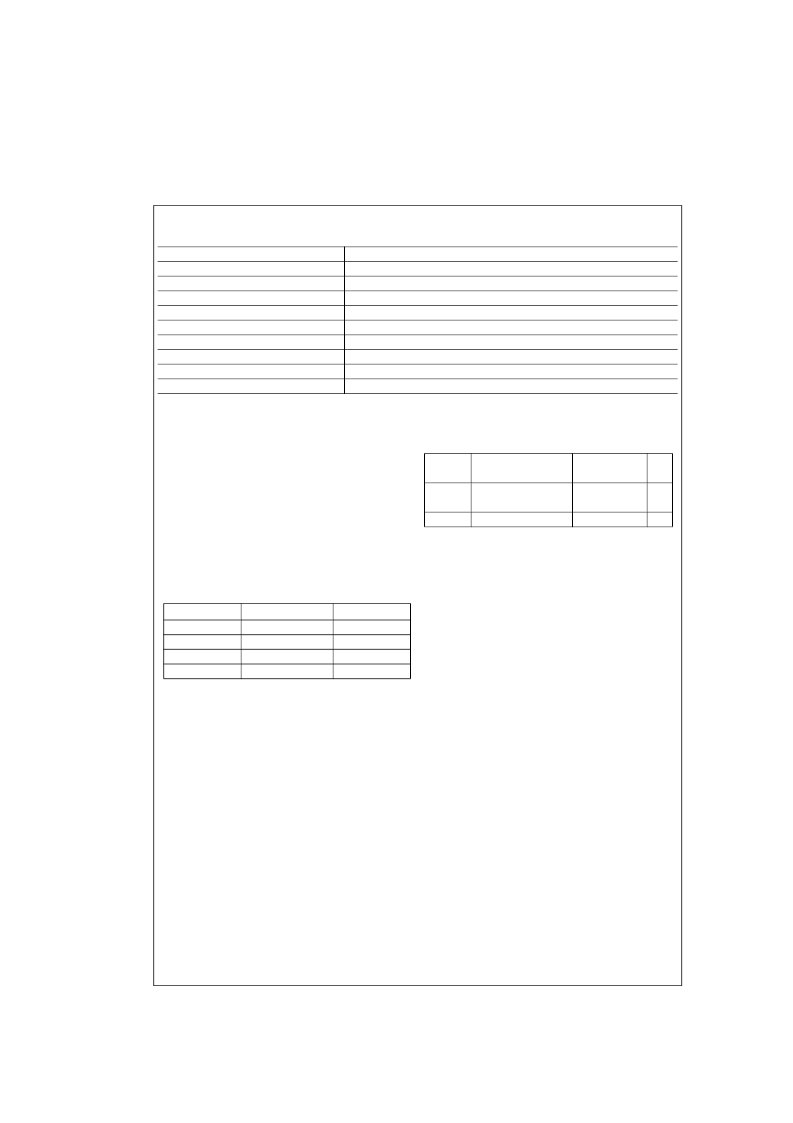

TABLE 7. Mode Register Control of LSPN

X

=

don

’

t care

Register

=

SCANPSC110F instruction register or any of the SCANPSC110F test data registers

PAD

=

insertion of a 1-bit register for synchronization

Mode Register

The mode register is an 8-bit data register used primarily to

configure the Local Scan Port Network. The mode register

is initialized to

“

00000001

”

binary upon entering the

Test-

Logic-Reset

state.

Bits 0, 1, 2, and 4 are used for scan chain configuration as

described in Table 7. When the

UNPARK

instruction is exe-

cuted, the scan chain configuration will be as shown in

Table 7 above. When all LSPs are parked, the scan chain

configuration

TDI

B

→

SCANPSC110F register

→

TDO

B

. Bit 3 is used for

TCK

Ln

configuration, see Table 8.

will

be

TABLE 8. Test Clock Configuration

Bit 3 is normally set to logic

“

0

”

so that TCK

L

is free-running

when the local scan ports are parked. When the local ports

are parked, bit 3 can be programmed with logic

“

1

”

, forcing

all of the LSP TCK

L

's to stop. This feature can be used in

power sensitive applications to reduce the power con-

sumed by the test circuitry in parts of the system that are

not under test.

Bit 3 of the mode register must be reset

to logic “0” before the UNPARK instruction is exe-

cuted.

Bit 7 is a status bit for the TCK counter. When the counter

is on and has reached terminal count (Zero) Bit 7 of the

mode register will be high (logic

“

1

”

). Bit 7 is read-only and

will be LOW in all other conditions.

Bits 5 and 6 are reserved for future use.

Device Identification Register

The device identification register (IDREG) is a 32-bit regis-

ter compliant with IEEE Std. 1149.1. When the

IDCODE

instruction is active, the identification register is loaded with

the value

“

0FC0E01F

”

Hex upon leaving the

Capture-DR

state (on the rising edge of the TCK

B

).

TABLE 9. Detailed Device Identification (Binary)

Linear Feedback Shift Register

The SCANPSC110F contains a

“

signature compactor

”

which supports test result evaluation in a multi-chain envi-

ronment. The signature compactor consists of a 16-bit lin-

ear-feedback shift register (LFSR) which can monitor local-

port scan data as it is shifted

“

upstream

”

from the

SCANPSC110F's local-port network. Once the LFSR is

enabled, the LFSR's state changes in a reproducible way

as each local-port data bit is shifted in from the local-port

network. When all local-port data has been scanned in, the

LFSR contains a 16-bit signature value which can be com-

pared against a signature computed for the expected

results vector.

The LFSR uses the following feedback polynomial:

F (x)

=

X

16

+

X

12

+

X

3

+

X

+

1

This signature compactor is used to compress serial data

shifted in from the local scan chain, into a 16-bit signature.

This signature can then be shifted out for comparison with

an expected value. This allows users to test long scan

chains in parallel, via Broadcast or Multi-Cast addressing

modes, and check only the 16-bit signatures from each

module.

The LFSR is initialized with a value of

“

0000

”

Hex upon

reset.

32-Bit TCK Counter Register:

The 32-bit TCK counter register enables BIST testing that

requires

“

n

”

TCK cycles, to be run on a parked LSP while

another SCANPSC110F port is being tested. The

CNTR-

SEL

instruction can be used to load a count-down value

into the counter register via the active scan chain. When

the counter is enabled (via the

CNTRON

instruction), and

the LSP is parked, the local TCKs will stop and be held

LOW when terminal count is reached.

The TCK counter is initialized with a value of

“

00000000

”

Hex upon reset.

Mode Register

XXX0X000

XXX0X001

XXX0X010

XXX0X011

XXX0X100

XXX0X101

XXX0X110

XXX0X111

XXX1XXXX

Scan Chain Configuration (If unparked)

TDI

B

→

Register

→

TDO

B

TDI

B

→

Register

→

LSP

1

→

PAD

→

TDO

B

TDI

B

→

Register

→

LSP

2

→

PAD

→

TDO

B

TDI

B

→

Register

→

LSP

1

→

PAD

→

LSP

2

→

PAD

→

TDO

B

TDI

B

→

Register

→

LSP

3

→

PAD

→

TDO

B

TDI

B

→

Register

→

LSP

1

→

PAD

→

LSP

3

→

PAD

→

TDO

B

TDI

B

→

Register

→

LSP

2

→

PAD

→

LSP

3

→

PAD

→

TDO

B

TDI

B

→

Register

→

LSP

1

→

PAD

→

LSP

2

→

PAD

→

LSP

3

→

PAD

→

TDO

B

TDI

B

→

Register

→

TDO

B

(Loopback)

Bit 3

LSP

n

TCK

Ln

1

0

1

0

Parked

Parked

Unparked

Unparked

Stop

Run

Run

Run

Bits

31–28

Version

Bits

27–12

Bits

11–1

Bit

0

1

Part Number

Manufacturer

Identity

0000 0001 111

0000

1111 1100 0000 1110

1

相關PDF資料 |

PDF描述 |

|---|---|

| SCP-5453 | SOCKET,IC,16PIN,MACHINE TOOLED WIRE WRAP,0.3"WIDE,0.515"LEAD |

| SCP-6122 | POWER OPERATIONAL AMPLIFIER |

| SCS152 | HM Series Hermetically Sealed Basic Switch, Single Pole Double Throw Circuitry, 0.5 A at 28 Vdc, Integral Lever Actuator, Solder Termination |

| SCS152-IS | Small glass bead with axial leads |

| SCS152-IW | Small glass bead with axial leads |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| SCANPSC110FSCX | 功能描述:特定功能邏輯 SCAN JTAG Port RoHS:否 制造商:Texas Instruments 產(chǎn)品: 系列:SN74ABTH18502A 工作電源電壓:5 V 封裝 / 箱體:LQFP-64 封裝:Tube |

| SCANSTA101 | 制造商:NSC 制造商全稱:National Semiconductor 功能描述:Low Voltage IEEE 1149.1 STA Master |

| SCANSTA101_06 | 制造商:NSC 制造商全稱:National Semiconductor 功能描述:Low Voltage IEEE 1149.1 STA Master |

| SCANSTA101SM | 功能描述:接口 - 專用 RoHS:否 制造商:Texas Instruments 產(chǎn)品類型:1080p60 Image Sensor Receiver 工作電源電壓:1.8 V 電源電流:89 mA 最大功率耗散: 最大工作溫度:+ 85 C 安裝風格:SMD/SMT 封裝 / 箱體:BGA-59 |

| SCANSTA101SM/NOPB | 功能描述:接口 - 專用 Low Vltg IEEE 1149.1 Sys Test Access RoHS:否 制造商:Texas Instruments 產(chǎn)品類型:1080p60 Image Sensor Receiver 工作電源電壓:1.8 V 電源電流:89 mA 最大功率耗散: 最大工作溫度:+ 85 C 安裝風格:SMD/SMT 封裝 / 箱體:BGA-59 |

發(fā)布緊急采購,3分鐘左右您將得到回復。