- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄384759 > MT90221AL (Mitel Networks Corporation) Quad IMA/UNI PHY Device PDF資料下載

參數(shù)資料

| 型號(hào): | MT90221AL |

| 廠商: | Mitel Networks Corporation |

| 英文描述: | Quad IMA/UNI PHY Device |

| 中文描述: | 四IMA的/單向物理層設(shè)備 |

| 文件頁(yè)數(shù): | 28/114頁(yè) |

| 文件大?。?/td> | 304K |

| 代理商: | MT90221AL |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)當(dāng)前第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)第69頁(yè)第70頁(yè)第71頁(yè)第72頁(yè)第73頁(yè)第74頁(yè)第75頁(yè)第76頁(yè)第77頁(yè)第78頁(yè)第79頁(yè)第80頁(yè)第81頁(yè)第82頁(yè)第83頁(yè)第84頁(yè)第85頁(yè)第86頁(yè)第87頁(yè)第88頁(yè)第89頁(yè)第90頁(yè)第91頁(yè)第92頁(yè)第93頁(yè)第94頁(yè)第95頁(yè)第96頁(yè)第97頁(yè)第98頁(yè)第99頁(yè)第100頁(yè)第101頁(yè)第102頁(yè)第103頁(yè)第104頁(yè)第105頁(yè)第106頁(yè)第107頁(yè)第108頁(yè)第109頁(yè)第110頁(yè)第111頁(yè)第112頁(yè)第113頁(yè)第114頁(yè)

MT90221

20

corresponding to the lowest link ID (LID) of the IMA

Group and placed in the RX UTOPIA FIFO. After a

complete cell read, a read pointer is set to the buffer

corresponding to the next LID. At the following IDCR

clock cycle, the next available cell is read. ICP cells

are skipped and Filler cells are discarded. This

operation is done in a RoundRobin fashion based on

the LID value for each IMA Group link. Faulty

conditions (i.e., buffer overflow, excessive delay) are

reported through the

IRQ Link Status

and

IRQ

UTOPIA Status

registers.

3.3.10 Delay Between Links

The delay values between links are reflecting the

various transit delays though the network. In order to

rebuild the original ATM cell sequence, the link that

exhibits less transport delay has to be stored until

the data from the slowest link (link having the largest

transport delay) has arrived. The link that exhibits

the largest transport delay will be the link that

requires the least cells to be stored. Conversely, the

line that exhibits the least transport delay is the link

that requires the largest number of cells to be stored.

Indirect access is provided to internal registers which

hold the various link delay values. The link number

and delay type are first selected by writing to the

RX

Delay Select

register. After 2 system clock cycles,

the 14-bit value in the

RX Delay MSB

and

LSB

and

the

RX Delay Link Number

registers are updated

and can be read. The valid delay types are: the

Maximum Delay over Time

,

the Current Maximum

Delay

and

the Current Minimum Delay

for an IMA

group and the

Current Delay

values for any links.

The delay values can be converted to time values by

multiplying the number of cells by the conversion

factor listed in the Table 5.

3.3.10.1 RX Recombiner Delay Value

The ICP Cell from each link of the same IMA Group

is used to determine the external SRAM read and

write pointers. The distance between the read and

write pointers is referred to as the recombiner delay.

Setting the recombiner delay to the maximum

acceptable delay results in a fixed recombiner delay

that is not optimum. For example, setting recombiner

delay to 25 msec when the worst case delay is 12

msec results in an additional, unnecessary delay of

13 msec.

The minimum recombiner delay would be the current

worst case differential delay. In the example above,

the recombiner delay would be set to 12 msec. In

this case, a link with larger transport delay than the

current worst value cannot be added to an existing

IMA group: the cells from this slower link have not

arrived when the cells sequence is rebuilt, as the

read pointer was set using the previous worst case

link. If this slower link is to be added, then the

recombiner process has to stop for the time required

to receive the cells on the slower link and then the

recombiner process can resume. This causes

disruption in the operation of the recombiner and will

affect the Cell Delay Variation (CDV).

To provide an optimal recombiner delay, the

MT90221 adds a guardband delay to the current

worst case recombination delay when the IMA Group

is first started up. Guardband delay is programmable

and minimizes the number of disruptions that would

otherwise occur in accommodating link delays

exceeding the current worst case. The guardband

delay is added to the minimum recombiner delay,

when the recombiner process is enabled for the first

link of an IMA group. The operational delay

corresponds to the guardband delay added to the

current worst case delay value.

The guardband delay value is specified for each IMA

group by writing to the

Guardband/Delta Delay

register. It should be the smallest value possible

consistent with minimizing the disruptions and the

smallest allowed value is 4. When operational, the

value of the guardband delay corresponds to the

delay value of the link having the greater transport

delay (the link where the data is the last to arrive to

the MT90221).

3.3.10.2 RX Maximum Operational Delay Value

The various delays on links of the same IMA Group

are measured and compared to the programmed

’maximum allowable value’ stored in the

Maximum Operational Delay

register for the IMA

Group. This value corresponds to the worst delay

value that is expected. This value cannot be larger

than the number of cells that can be stored in the

external memory. The smallest ’maximum allowable

value’ is four cells. These values are independently

established for each of the four IMA Groups.

RX

3.3.10.3 Link Out of Delay Synchronization (LODS)

If a link to be added is slower and cannot be

accommodated by the present guardband, an LODS

signal is generated and the link delay value is

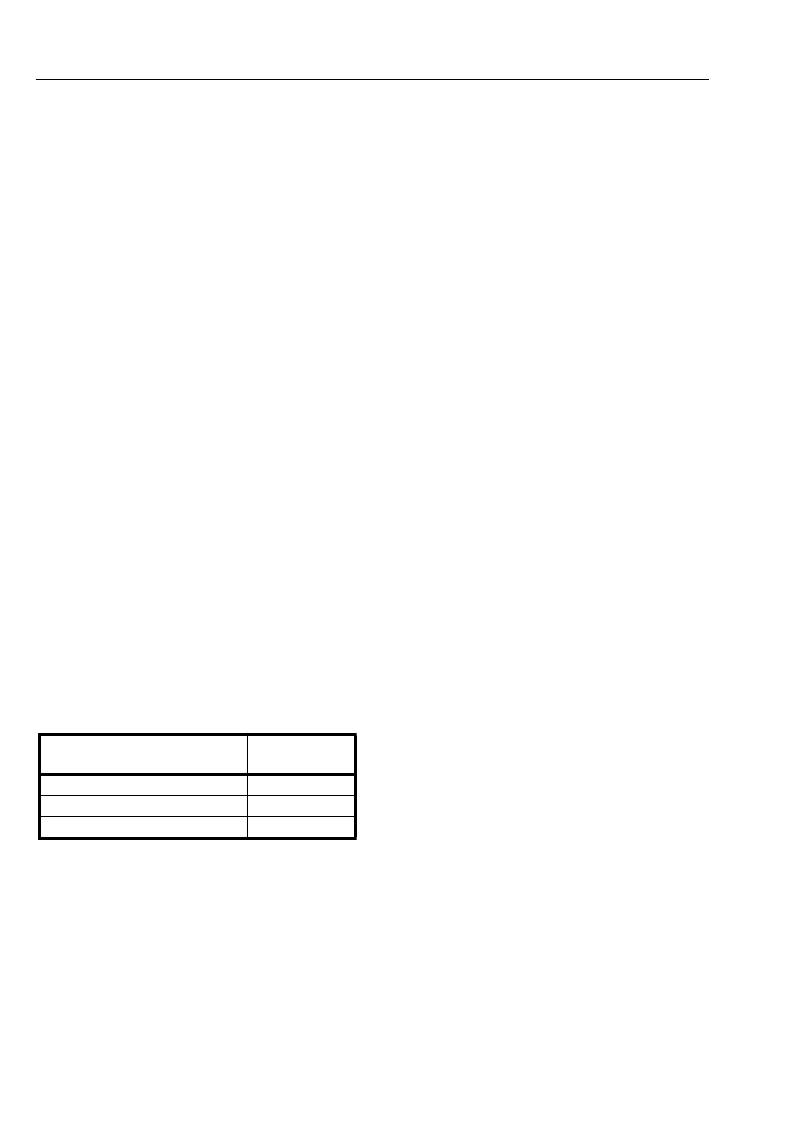

Link Type

Time per cell

(msec)

T1 ISDN (23 ch. per frame)

T1 (24 ch. per frame)

E1 (30 ch. per frame)

Table 5 - Conversion Factors Time/Cell

(msec)

0.288

0.276

0.221

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| MT9041B | T1/E1 System Synchronizer |

| MT9041BP | T1/E1 System Synchronizer |

| MT9041 | Multiple Output Trunk PLL |

| MT9041AP | IC REG LDO 150MA 5.0V 0.5% 8SOIC |

| MT9042C | Multitrunk System Synchronizer |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| MT90222 | 制造商:ZARLINK 制造商全稱(chēng):Zarlink Semiconductor Inc 功能描述:4/8/16 Port IMA/TC PHY Device |

| MT90222AG | 制造商:Microsemi Corporation 功能描述:ATM IMA 40MBPS 2.5V 384BGA - Trays |

| MT90222AG2 | 制造商:Microsemi Corporation 功能描述:ATM IMA 40MBPS 2.5V 384BGA /BAKE/DRYPACK - Trays |

| MT90223AG | 制造商:Microsemi Corporation 功能描述:ATM IMA 80MBPS 2.5V 384BGA - Trays |

| MT90223AG2 | 制造商:Microsemi Corporation 功能描述:ATM IMA 80MBPS 2.5V 384BGA - Trays |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。