- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄296460 > MAX1359ACTL+ (MAXIM INTEGRATED PRODUCTS INC) SPECIALTY ANALOG CIRCUIT, QCC40 PDF資料下載

參數(shù)資料

| 型號: | MAX1359ACTL+ |

| 廠商: | MAXIM INTEGRATED PRODUCTS INC |

| 元件分類: | 模擬信號調(diào)理 |

| 英文描述: | SPECIALTY ANALOG CIRCUIT, QCC40 |

| 封裝: | 6 X 6 MM, 0.80 MM HEIGHT, MO220, TQFN-40 |

| 文件頁數(shù): | 25/74頁 |

| 文件大小: | 1214K |

| 代理商: | MAX1359ACTL+ |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁當(dāng)前第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁

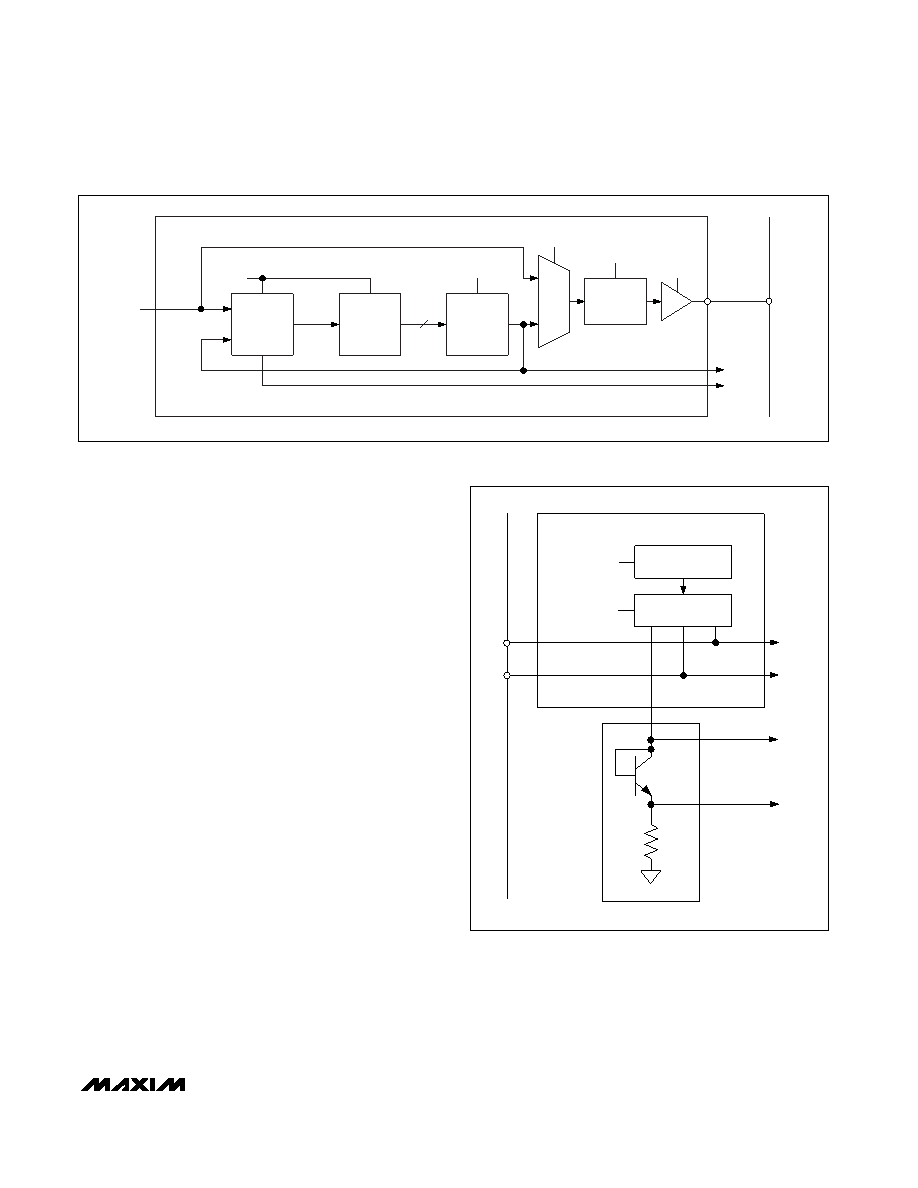

High-Frequency Clock

An internal oscillator and a frequency-locked loop (FLL)

are used to generate a 4.9152MHz ±1% high-frequen-

cy clock. This clock and derivatives are used internally

by the ADC, analog switches, and PWM. This clock sig-

nal outputs to CLK. When the FLL is enabled, the high-

frequency clock is locked to the 32.768kHz reference. If

the FLL is disabled, the high-frequency clock is free-

running. At power-up, the CLK pin defaults to a

2.4576MHz clock output, which is compatible with most

Cs. See Figure 14 for a block diagram of the high-fre-

quency clock.

User-Programmable I/Os

The MAX1358/MAX1359/MAX1360 provide four digital

programmable I/Os (UPIO1–UPIO4). Configure UPIOs

as logic inputs or outputs using the UPIO control regis-

ter. Configure the internal pullups using the UPIO setup

register, if required. At power-up, the UPIO’s are inter-

nally pulled up to DVDD. UPIO_ outputs can be refer-

enced to DVDD or CPOUT. See the UPIO__CTRL

Register and UPIO_SPI Register sections for more

details on configuring the UPIO_ pins.

Program each UPIO1–UPIO4 as one of the following:

General-purpose input

Power-mode control

Analog switch (SPST) and SPDT control input

ADC data-ready output

General-purpose output

PWM output

Alarm output

SPI passthrough

MAX1358/MAX1359/MAX1360

16-Bit Data-Acquisition Systems with ADC, DACs,

UPIOs, RTC, Voltage Monitors, and Temp Sensor

______________________________________________________________________________________

31

M32K

TUNE<8:0>

HFCE

FLLE

CRDY

HFCLK

1, 2, 4, 8

DIVIDER

2:1

MUX

CLK

CLKE

CKSEL<1:0>

CKSEL2

1

0

4.9152MHz HF OSCILLATOR AND FLL

4.9152MHz

32.768kHz

FREQUENCY

COMPARE

FREQ

ERROR

DIGITALLY

CONTROLLED

OSCILLATOR

FREQUENCY

INTEGRATOR

Figure 14. High-Frequency Clock and FLL Block Diagram

Figure 15. Temperature-Sensor Measurement Block Diagram

CURRENT

SOURCE

1:3

DEMUX

IVAL<1:0>

IMUX<1:0>

AIN1

AIN2

AIN1

AIN2

TEMP+

TEMP-

PROGRAMMABLE CURRENT SOURCE

TEMP SENSOR

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| MAX16005AUE+ | 6-CHANNEL POWER SUPPLY MANAGEMENT CKT, PDSO16 |

| MAX16005DUE+ | 6-CHANNEL POWER SUPPLY MANAGEMENT CKT, PDSO16 |

| MAX16072RS30D3+ | POWER SUPPLY SUPPORT CKT, PBGA4 |

| MAX17004AETJ+ | 3.3 A DUAL SWITCHING CONTROLLER, 575 kHz SWITCHING FREQ-MAX, QCC32 |

| MAX177ENG | CMOS 10-Bit A/D Converter with Track-and-Hold |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| MAX1359ACTL+ | 制造商:Maxim Integrated Products 功能描述:DATA ACQ SYS SGL ADC SGL DAC 16BIT 40TQFN EP - Rail/Tube |

| MAX1359ACTL+T | 制造商:Maxim Integrated Products 功能描述:DATA ACQ SYS SGL ADC SGL DAC 16BIT 40TQFN EP - Tape and Reel |

| MAX1359ACTL-T | 制造商:Maxim Integrated Products 功能描述:16-BIT DATA-ACQUISITION SYSTEM W ADC,DACS,UPI - Tape and Reel |

| MAX1359AEGL | 制造商:Maxim Integrated Products 功能描述:- Rail/Tube |

| MAX1359AETL | 制造商:Maxim Integrated Products 功能描述:16-BIT DATA-ACQUISITION SYSTEM W ADC,DACS,UPI - Rail/Tube |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。