- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄180243 > M7A3PE600-FPQG208I FPGA, 600000 GATES, PQFP208 PDF資料下載

參數(shù)資料

| 型號: | M7A3PE600-FPQG208I |

| 元件分類: | FPGA |

| 英文描述: | FPGA, 600000 GATES, PQFP208 |

| 封裝: | 0.50 MM PITCH, GREEN, PLASTIC, QFP-208 |

| 文件頁數(shù): | 46/168頁 |

| 文件大?。?/td> | 1335K |

| 代理商: | M7A3PE600-FPQG208I |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁當前第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁第107頁第108頁第109頁第110頁第111頁第112頁第113頁第114頁第115頁第116頁第117頁第118頁第119頁第120頁第121頁第122頁第123頁第124頁第125頁第126頁第127頁第128頁第129頁第130頁第131頁第132頁第133頁第134頁第135頁第136頁第137頁第138頁第139頁第140頁第141頁第142頁第143頁第144頁第145頁第146頁第147頁第148頁第149頁第150頁第151頁第152頁第153頁第154頁第155頁第156頁第157頁第158頁第159頁第160頁第161頁第162頁第163頁第164頁第165頁第166頁第167頁第168頁

ProASIC3E Flash Family FPGAs

2- 2

A dvanced v0. 5

Device Overview

The ProASIC3E device family consists of five distinct

programmable architectural features (Figure 2-2):

Core Architecture

VersaTile

The proprietary ProASIC3E family architecture provides

granularity comparable to gate arrays. The ProASIC3E

device core consists of a sea-of-VersaTiles architecture.

As illustrated in Figure 2-3 on page 2-3, there are four

inputs in a logic VersaTile cell, and each VersaTile can be

configured

using

the

appropriate

Flash

switch

connections:

Any three-input logic function

Latch with clear or set

D-flip-flop with clear or set

Enable D-flip-flop with clear or set (on a fourth

input)

VersaTiles can flexibly map the logic and sequential gates

of a design. The inputs of the VersaTile can be inverted

(allowing bubble pushing), and the output of the tile can

connect to high-speed, very-long-line routing resources.

VersaTiles and larger functions can be connected with

any of the four levels of routing hierarchy.

When the VersaTile is used as an enable D-flip-flop, SET/

CLR is supported by a fourth input. The SET/CLR signal

can only be routed to this fourth input over the VersaNet

(global) network. However, if in the user’s design the

SET/CLR signal is not routed over the VersaNet network,

a compile warning message will be given and the

intended logic function will be implemented by two

VersaTiles instead of one.

The output of the VersaTile is F2 (Figure 2-3 on page 2-3)

when the connection is to the ultra-fast local lines, or YL

when the connection is to the efficient long-line or very-

long-line resources.

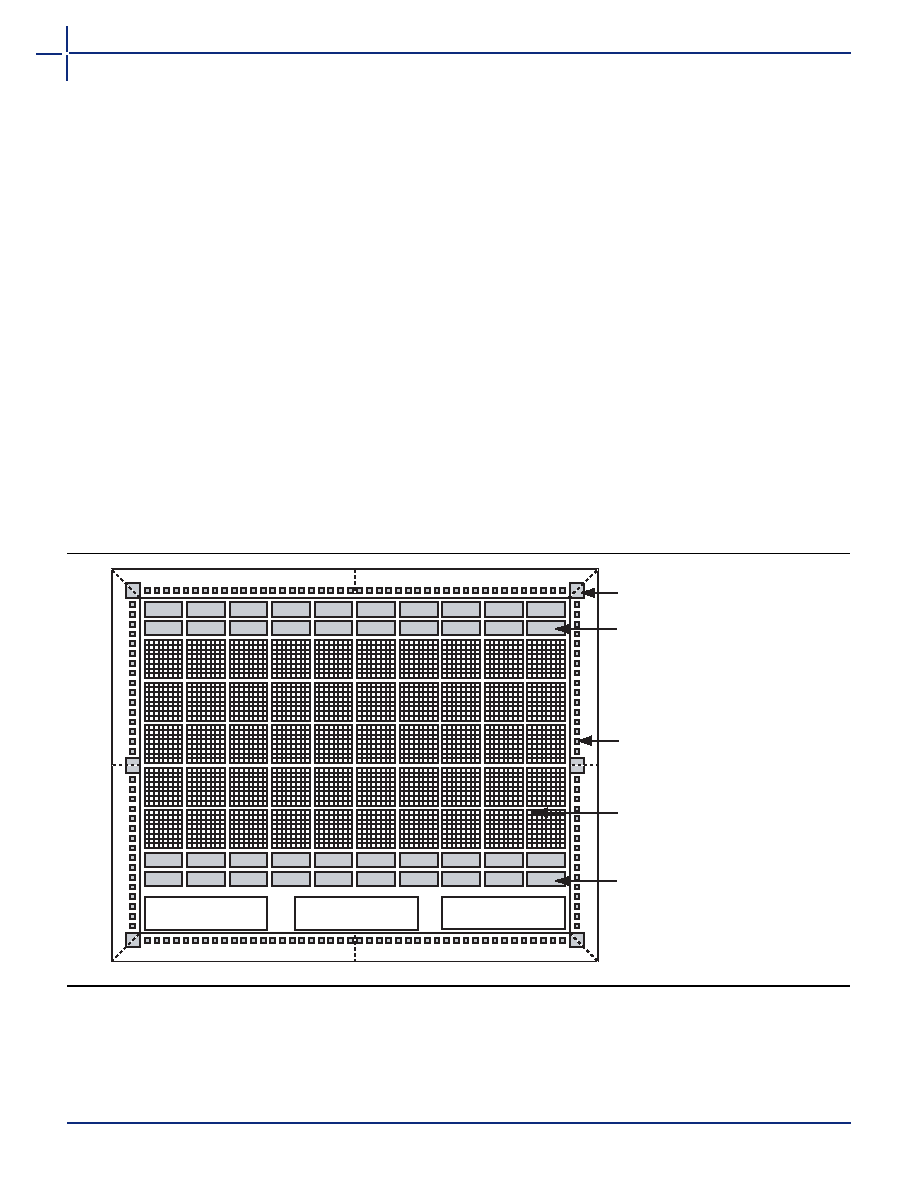

Figure 2-2 Device Architecture Overview

4,608-Bit Dual-Port SRAM

or FIFO Block

VersaTile

RAM Block

CCC

I/Os

4,608-Bit Dual-Port SRAM

or FIFO Block

ISP AES

Decryption

User Nonvolatile

FlashROM

Charge Pumps

Bank 0

Bank

7

Bank

6

Bank

3

Bank

2

Bank 1

Bank 5

Bank 4

相關PDF資料 |

PDF描述 |

|---|---|

| M7R-R63FAJFREQ | CRYSTAL OSCILLATOR, CLOCK, 80.001 MHz - 125 MHz, CMOS/TTL OUTPUT |

| M7R-R68TAJFREQ | CRYSTAL OSCILLATOR, CLOCK, 80.001 MHz - 125 MHz, CMOS/TTL OUTPUT |

| M7R76FCJFREQ | CRYSTAL OSCILLATOR, CLOCK, 80.001 MHz - 125 MHz, CMOS OUTPUT |

| M7R-R53FCJFREQ | CRYSTAL OSCILLATOR, CLOCK, 80.001 MHz - 125 MHz, CMOS OUTPUT |

| M7R-R16FAJFREQ | CRYSTAL OSCILLATOR, CLOCK, 80.001 MHz - 125 MHz, CMOS/TTL OUTPUT |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| M7A5 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:MEDIUM CURRENT SILICON RECTIFIERS |

| M7A9 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:MEDIUM CURRENT SILICON RECTIFIERS |

| M7AFS600-1FG256 | 制造商:Microsemi Corporation 功能描述:FPGA FUSION 600K GATES 1282.05MHZ 130NM 1.5V 256FBGA - Trays 制造商:Microsemi SOC Products Group 功能描述:FPGA FUSION 600K GATES 1282.05MHZ 130NM 1.5V 256FBGA - Trays |

| M7AFS600-1FG256ES | 制造商:ACTEL 制造商全稱:Actel Corporation 功能描述:Actel Fusion Mixed-Signal FPGAs |

| M7AFS600-1FG256I | 制造商:Microsemi Corporation 功能描述:FPGA FUSION 600K GATES 1282.05MHZ 130NM 1.5V 256FBGA - Trays 制造商:Microsemi SOC Products Group 功能描述:FPGA FUSION 600K GATES 1282.05MHZ 130NM 1.5V 256FBGA - Trays |

發(fā)布緊急采購,3分鐘左右您將得到回復。