- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄370782 > HYB18T512160AF (INFINEON TECHNOLOGIES AG) 512-Mbit DDR2 SDRAM PDF資料下載

參數(shù)資料

| 型號(hào): | HYB18T512160AF |

| 廠商: | INFINEON TECHNOLOGIES AG |

| 英文描述: | 512-Mbit DDR2 SDRAM |

| 中文描述: | 512兆位DDR2 SDRAM的 |

| 文件頁(yè)數(shù): | 34/117頁(yè) |

| 文件大?。?/td> | 2102K |

| 代理商: | HYB18T512160AF |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)當(dāng)前第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)第69頁(yè)第70頁(yè)第71頁(yè)第72頁(yè)第73頁(yè)第74頁(yè)第75頁(yè)第76頁(yè)第77頁(yè)第78頁(yè)第79頁(yè)第80頁(yè)第81頁(yè)第82頁(yè)第83頁(yè)第84頁(yè)第85頁(yè)第86頁(yè)第87頁(yè)第88頁(yè)第89頁(yè)第90頁(yè)第91頁(yè)第92頁(yè)第93頁(yè)第94頁(yè)第95頁(yè)第96頁(yè)第97頁(yè)第98頁(yè)第99頁(yè)第100頁(yè)第101頁(yè)第102頁(yè)第103頁(yè)第104頁(yè)第105頁(yè)第106頁(yè)第107頁(yè)第108頁(yè)第109頁(yè)第110頁(yè)第111頁(yè)第112頁(yè)第113頁(yè)第114頁(yè)第115頁(yè)第116頁(yè)第117頁(yè)

HYB18T512[40/80/16]0AF–[3/3S/3.7/5]

512-Mbit DDR2 SDRAM

Functional Description

Data Sheet

34

Rev. 1.3, 2005-01

09112003-SDM9-IQ3P

3.10

Extended Mode Register EMR(2)

The Extended Mode Registers EMR(2) and EMR(3)

are reserved for future use and must be programmed

when setting the mode register during initialization.The

extended mode register EMR(2) is written by asserting

LOW on CS, RAS, CAS, WE, BA0 and HIGH on BA1,

while controlling the states of the address pins. The

DDR2 SDRAM should be in all bank precharge with

CKE already high prior to writing into the extended

mode register. The mode register set command cycle

time (

t

MRD

) must be satisfied to complete the write

operation to the EMR(2). Mode register contents can

be changed using the same command and clock cycle

requirements during normal operation as long as all

banks are in precharge state.

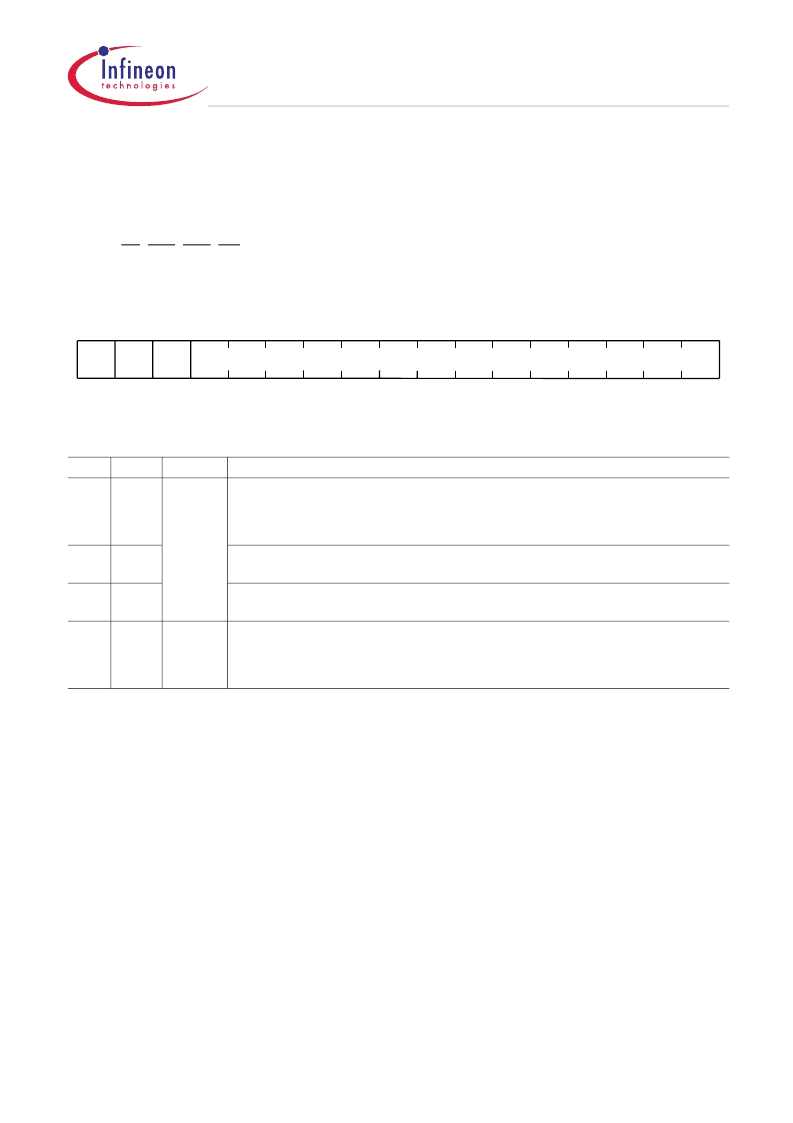

Table 11

Field

BA2

EMRS(2) Programming Extended Mode register Definition (BA[2:0]=010

B

)

Type

1)

Description

reg.addr

Bank Address[2]

Note:BA2 is not available on 256Mbit and 512Mbit components

Bits

16

1) w = write only

0

B

Bank Adress[1]

1

B

BA1

, Bank Address

Bank Adress[0]

0

B

BA0

, Bank Address

Address Bus[13:0]

Note:A13 is not available for 256 Mbit and x16 512 Mbit configuration

BA2

, Bank Address

BA1

15

BA0

14

A

[13:0]

w

0

B

A[13:0]

, Address bits

-0"4

"! " ! " ! !

!

!

!

!

!

!

!

!

!

!

!

!

!

REG ADDR

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| HYB18T512160AF-3 | 512-Mbit DDR2 SDRAM |

| HYB18T512160AF-3.7 | 512-Mbit DDR2 SDRAM |

| HYB18T512160AF-3S | 512-Mbit DDR2 SDRAM |

| HYB18T512400AF-3 | 512-Mbit DDR2 SDRAM |

| HYB18T512400AF-3S | 512-Mbit DDR2 SDRAM |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| HYB18T512161BF-25 | 制造商:Qimonda 功能描述:SDRAM, DDR, 32M x 16, 84 Pin, Plastic, BGA |

| HYB18T512400AF-5 | 制造商:Intersil Corporation 功能描述:SDRAM, DDR, 128M x 4, 60 Pin, Plastic, BGA |

| HYB18T512400BF-3S | 制造商:Qimonda 功能描述: |

| HYB18T512800AF-3S | 制造商:Qimonda 功能描述: 制造商:Infineon Technologies AG 功能描述:32M X 16 DDR DRAM, 0.45 ns, PBGA84 |

| HYB18T512800BF-2.5 | 功能描述:IC DDR2 SDRAM 512MBIT 60TFBGA RoHS:是 類別:集成電路 (IC) >> 存儲(chǔ)器 系列:- 標(biāo)準(zhǔn)包裝:60 系列:- 格式 - 存儲(chǔ)器:EEPROMs - 串行 存儲(chǔ)器類型:EEPROM 存儲(chǔ)容量:16K (2K x 8) 速度:2MHz 接口:SPI 3 線串行 電源電壓:2.5 V ~ 5.5 V 工作溫度:-40°C ~ 85°C 封裝/外殼:8-DIP(0.300",7.62mm) 供應(yīng)商設(shè)備封裝:8-PDIP 包裝:管件 產(chǎn)品目錄頁(yè)面:1449 (CN2011-ZH PDF) |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。