- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄166397 > B900J24PXX12I 0-BIT, 80 MHz, OTHER DSP, PQFP44 PDF資料下載

參數(shù)資料

| 型號: | B900J24PXX12I |

| 元件分類: | 數(shù)字信號處理 |

| 英文描述: | 0-BIT, 80 MHz, OTHER DSP, PQFP44 |

| 文件頁數(shù): | 76/100頁 |

| 文件大?。?/td> | 1547K |

| 代理商: | B900J24PXX12I |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁當前第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁

Advance Data Sheet

B900

July 1999

Baseband Signal Processor

Lucent Technologies Inc.

77

8 Timing Requirements and Characteristics

Requirements are restrictions on the external device connected to the B900. Characteristics are properties of the

B900. For details, see Section 6, Device Requirements and Characteristics, and Section 7, Electrical Require-

The characteristics listed are valid under the following conditions:

s

VSS = 0 V, VDD = 5.0 V ± 0.5 V, TA = 0 °C to 70 °C, CLOAD = 50 pF, TMIN = 10.0 ns

s

VSS = 0 V, VDD = 3.3 V ± 0.3 V, TA = –40 °C to +85 °C, CLOAD = 50 pF, TMIN = 12.5 ns

Output characteristics can be derated as a function of load capacitance (CL):

s

For all rising edge outputs, dt/dCL

≤ 0.06 ns/pF for 0 ≤ CL ≤ 100 pF at 2.0 V

s

For all falling edge outputs, dt/dCL

≤ 0.05 ns/pF for 0 ≤ CL ≤ 100 pF at 0.8 V

For example, the derating for a time delay that includes a rising edge with an external load of 20 pF is as follows:

t = (CL – CLOAD) dt/dCL = (20 – 50) 0.06 = –1.8 ns

Output characteristics assume standard slew rate buffers. See Table 44 on page 55 for information on mask

options, for slow buffers option all the output times should be increased by the additional time given by the

equation:

t = 0.4

CL

Where CL is the load capacitance in picofarads, and t is the additional output delay in nanoseconds. For example,

for load capacitance of 50 pF, with slow buffers option, all output timing characteristics should be increased by

20 ns.

For definitions of the VIH, VIL, VOH, and VOL labels, see Table 91 on page 72. In this section’s timing diagrams,

these labels distinguish inputs and outputs.

8.1

Input Clock Options

The input clocks to the B900 allow for the use of either CMOS level input signals or an internal crystal oscillator

with an external crystal. This allows the user to select either both clock inputs to use the internal crystal oscillator

or XTALA may be driven with a CMOS level signal. In the latter case, the OSCBYP pin should be pulled high

externally, while XTALB is terminated by a 20 pF capacitor.

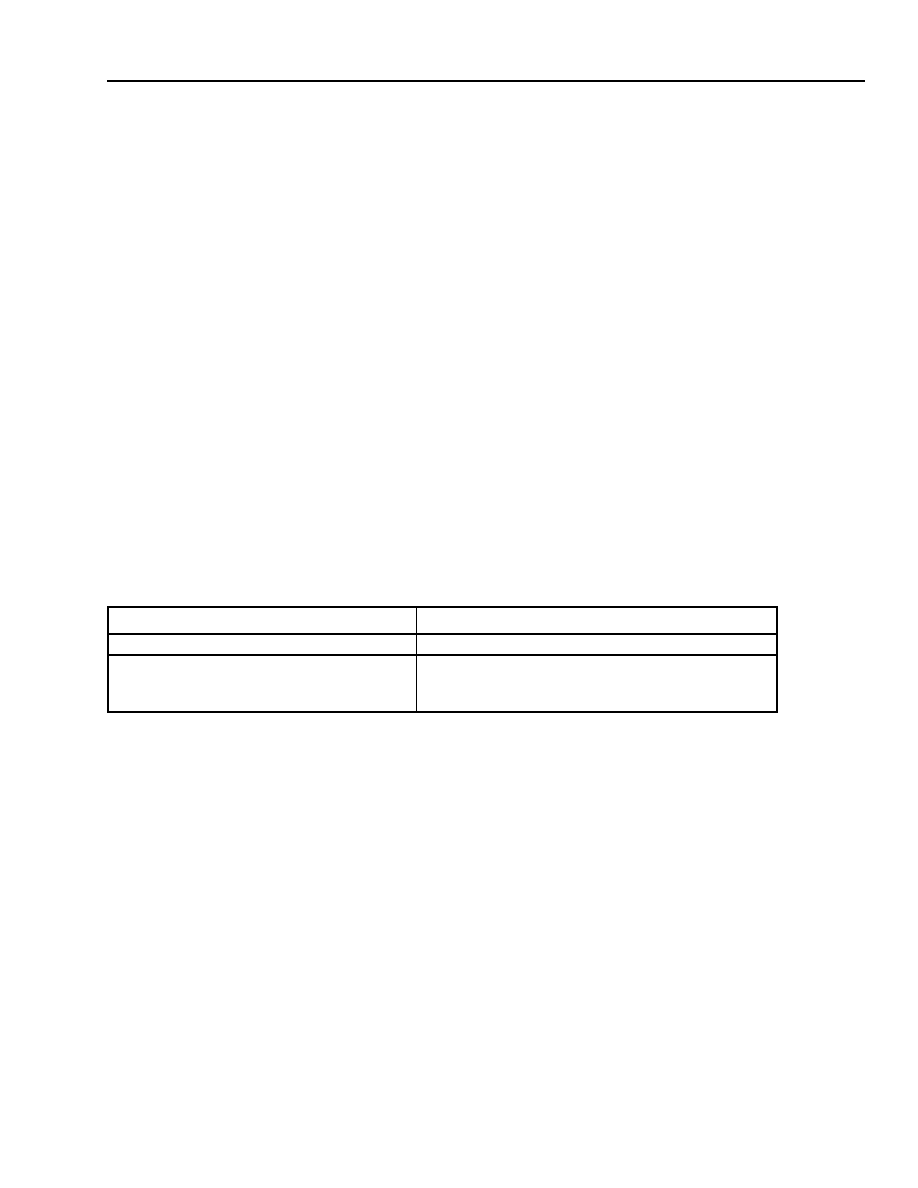

Table 98. Test Conditions

Test Conditions for Inputs

Test Conditions for Outputs

Rise and fall times of 4 ns or less.

CLOAD = 50 pF.

Timing reference levels for delays = VIH, VIL.

Timing reference levels for delays = VOH, VOL.

3-state delays are measured to the high-impedance

state of the output driver.

相關PDF資料 |

PDF描述 |

|---|---|

| B900J24FXX12IT | 0-BIT, 59.88 MHz, OTHER DSP, PQFP44 |

| BA00CC0WCP-V5 | 1A Low Dropout Voltage Regulator with Shut Down Switch(Adustable Voltage) |

| BA10E6 | COPPER ALLOY, TIN FINISH, RING TERMINAL |

| BA12004 | 0.5 A, 7 CHANNEL, NPN, Si, POWER TRANSISTOR |

| BA1518SUR5VP | SINGLE COLOR DISPLAY CLUSTER, ULTRA RED |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| B-900-M-10 | 制造商:Thomas & Betts 功能描述: |

| B-900-M-10-EG | 制造商:Thomas & Betts 功能描述: |

| B-900-M-20 | 制造商:Thomas & Betts 功能描述: |

| B-900-M-20-EG | 制造商:Thomas & Betts 功能描述: |

| B901 | 制造商:EDAL 制造商全稱:EDAL 功能描述:Silicon Bridge Rectifier |

發(fā)布緊急采購,3分鐘左右您將得到回復。