- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄1974 > XCF128XFTG64C (Xilinx Inc)IC PROM SRL 128M GATE 64-FTBGA PDF資料下載

參數(shù)資料

| 型號: | XCF128XFTG64C |

| 廠商: | Xilinx Inc |

| 文件頁數(shù): | 31/88頁 |

| 文件大小: | 0K |

| 描述: | IC PROM SRL 128M GATE 64-FTBGA |

| 標(biāo)準(zhǔn)包裝: | 1 |

| 可編程類型: | 系統(tǒng)內(nèi)可編程 |

| 存儲容量: | 128Mb |

| 電源電壓: | 1.7 V ~ 2 V |

| 工作溫度: | -40°C ~ 85°C |

| 封裝/外殼: | 64-TBGA |

| 供應(yīng)商設(shè)備封裝: | 64-TFBGA |

| 包裝: | 托盤 |

| 產(chǎn)品目錄頁面: | 601 (CN2011-ZH PDF) |

| 其它名稱: | 122-1578 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁當(dāng)前第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁

Platform Flash XL High-Density Configuration and Storage Device

DS617 (v3.0.1) January 07, 2010

Product Specification

37

R

Power-On Reset

To ensure a correct power-up sequence of Platform Flash

XL, the VDD ramp time, TVDDPOR, must not be shorter than

200

μs or longer than 50 ms during power-up (see Figure 18,

page 40). These timing limits correspond to the ramp rate

values for which the power-up current is in the range where

the VDD ramp time is formally characterized or tested.

The device requires that the VDD power supply

monotonically rises to the nominal operating voltage within

the specified VDD rise time. If the power supply cannot meet

this requirement, then the device might not perform power-

on reset properly.

During the POR sequence or a reset pulse (RP), the

READY_WAIT pin is held Low by the device. After the

required supply voltages (VDD and VDDQ) have reached

their respective POR thresholds, the READY_WAIT pin is

released after a minimum time of tRWL, to give the power

supplies an additional margin for them to stabilize before

initiating the configuration.

For systems using a slow-rising power supply, an additional

power-monitoring circuit can be used to delay the release of

the READY_WAIT pin.

If the power drops below the power-down threshold

(VDDPD), the device is reset and the READY_WAIT pin is

held Low again until the POR threshold is reached (see

Figure 18 for an illustration).

The power-up sequences with and without free-running

clock are represented in Figure 11, page 31 and Figure 17.

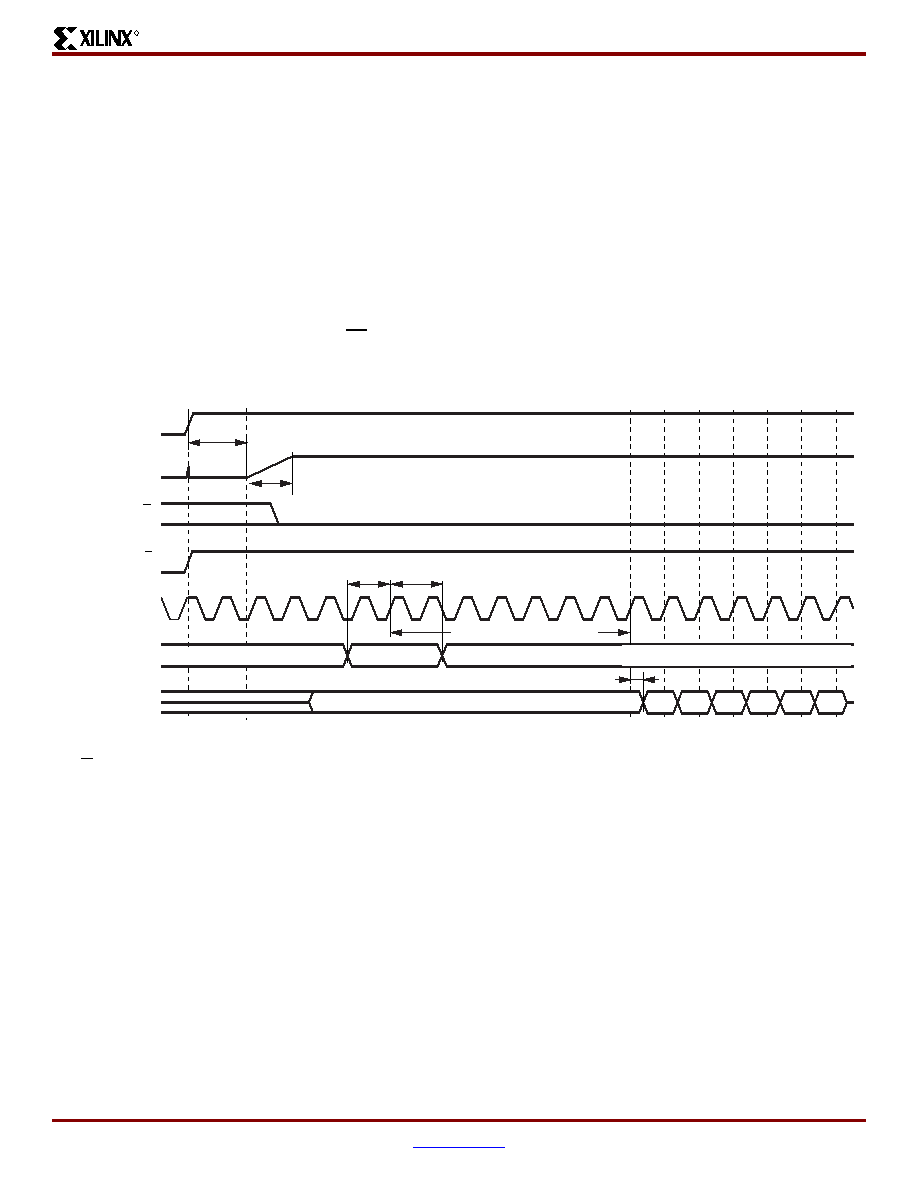

X-Ref Target - Figure 17

Notes:

1.

W is tied High.

Figure 17: Power-Up Sequence (System with Free-Running Clock)

K

V

DD/VDDQ

G

L

A22-A0

Valid Address

DQ15–DQ0

READY_WAIT

12

3

4

Latency Cycles (default = 7)

T

VHRWZ

T

AVKH3

T

KH3AX

T

KHQV

DS617_13_053008

T

RWRT

FFFFh (Sync + Dummy Cycle)

D0

D1

D2

D3

D4

D5

Address not Valid

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| XCF32PFS48C | IC PROM SRL 1.8V 32M 48CSBGA |

| XCR3256XL-7CS280C | IC CPLD 256MCELL 3.3V HP 280CSP |

| XCS10-3VQG100C | IC FPGA 5V C-TEMP 100-VQFP |

| XCV600E-8HQ240C | IC FPGA 1.8V C-TEMP 240-HQFP |

| XCV812E-8FG900C | IC FPGA 1.8V C-TEMP 900-FBGA |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| XCF128XFTG64CES | 制造商:Xilinx 功能描述: |

| XCF12-L4Z1 | 制造商:SAIA - BURGESS ELECTRONICS INC. 功能描述:Catalogue / XCF12-L4Z1 |

| XCF12-S1 | 制造商:SAIA - BURGESS ELECTRONICS INC. 功能描述:Catalogue / XCF12-S1 |

| XCF13-S1 | 制造商:SAIA - BURGESS ELECTRONICS INC. 功能描述:Catalogue / XCF13-S1 |

| XCF16P | 制造商:XILINX 制造商全稱:XILINX 功能描述:Platform Flash In-System Programmable Configuration PROMs |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。