- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄1974 > XCF128XFTG64C (Xilinx Inc)IC PROM SRL 128M GATE 64-FTBGA PDF資料下載

參數(shù)資料

| 型號(hào): | XCF128XFTG64C |

| 廠商: | Xilinx Inc |

| 文件頁(yè)數(shù): | 27/88頁(yè) |

| 文件大小: | 0K |

| 描述: | IC PROM SRL 128M GATE 64-FTBGA |

| 標(biāo)準(zhǔn)包裝: | 1 |

| 可編程類型: | 系統(tǒng)內(nèi)可編程 |

| 存儲(chǔ)容量: | 128Mb |

| 電源電壓: | 1.7 V ~ 2 V |

| 工作溫度: | -40°C ~ 85°C |

| 封裝/外殼: | 64-TBGA |

| 供應(yīng)商設(shè)備封裝: | 64-TFBGA |

| 包裝: | 托盤 |

| 產(chǎn)品目錄頁(yè)面: | 601 (CN2011-ZH PDF) |

| 其它名稱: | 122-1578 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)當(dāng)前第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)第69頁(yè)第70頁(yè)第71頁(yè)第72頁(yè)第73頁(yè)第74頁(yè)第75頁(yè)第76頁(yè)第77頁(yè)第78頁(yè)第79頁(yè)第80頁(yè)第81頁(yè)第82頁(yè)第83頁(yè)第84頁(yè)第85頁(yè)第86頁(yè)第87頁(yè)第88頁(yè)

Platform Flash XL High-Density Configuration and Storage Device

DS617 (v3.0.1) January 07, 2010

Product Specification

33

R

The Clock signal is then halted at VIH or at VIL, and Output

Enable (G) goes High. When Output Enable goes Low

again and the Clock signal restarts, the Synchronous Burst

Read operation is resumed at its previous location.

When READY_WAIT (with CR4 = ‘0’) is gated by E, it

reverts to high impedance when G goes High.

See Table 29, page 52, and Figure 30, page 54 for details.

Single Synchronous Read Mode

Single Synchronous Read operations are similar to

Synchronous Burst Read operations except that the

memory outputs the same data to the end of the operation.

Synchronous Single Reads are used to read the Electronic

Signature, Status Register, CFI, Block Protection Status,

Configuration Register Status, or Protection Register. When

the addressed bank is in Read CFI, Read Status Register,

or Read Electronic Signature mode, the READY_WAIT

signal (if configured for the Wait function with CR4 = ‘0’) is

asserted during X-latency, the WAIT state and at the end of

a 4, 8 and 16-word burst. The signal is only deasserted

when output data is valid. See Table 29, page 52 and

Figure 27, page 51, for details.

Dual Operations and Multiple Bank Architecture

The Multiple Bank Architecture of Platform Flash XL gives

greater flexibility for software developers to split the code

and data spaces within the memory array. The Dual

Operations feature simplifies the software management of

the device by allowing code to be executed from one bank

while another bank is being programmed or erased. This

feature allows read operations with zero latency in one bank

while programming or erasing in another bank.

Note: Only one bank at a time is allowed to be in program or

erase mode.

If a read operation is required in a bank which is

programming or erasing, the program or erase operation

can be suspended. Also if the suspended operation is

erase, then a program command can be issued to another

block so that the device can have one block in Erase

Suspend mode, one in programming mode, and other

banks in read mode.

Bus Read operations are allowed in other banks between

setup and confirm cycles of program or erase operations.

By using a combination of these features, read operations

are always possible in Platform Flash XL.

Table 15 and Table 16, page 35 show which dual operations

are possible in other banks and in the same bank.

Dual operations between the Parameter Bank and either of

the CFI, OTP, or Electronic Signature memory spaces are

not allowed. Table 17, page 36 shows which dual

operations are allowed or not between the CFI, OTP,

Electronic Signature locations and the memory array.

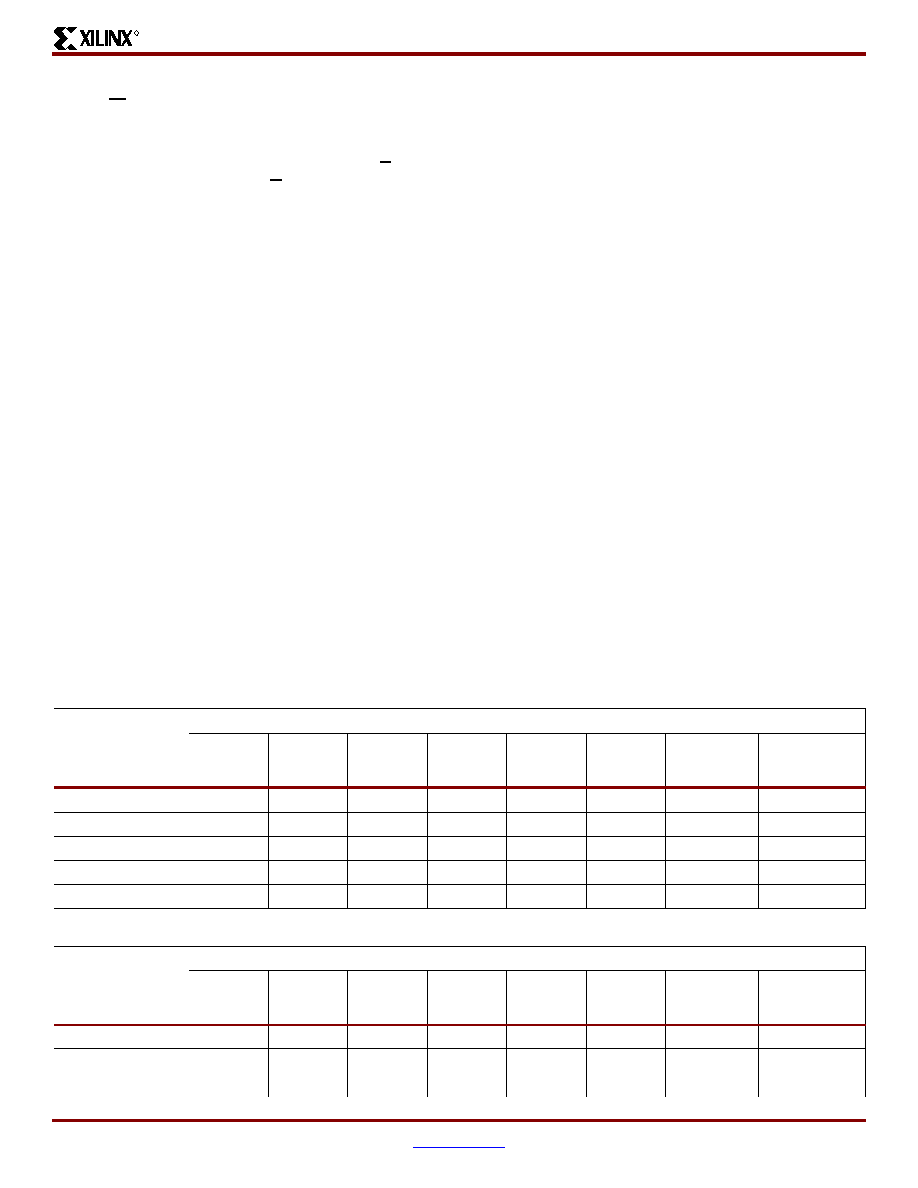

Table 15: Dual Operations Allowed in Another Bank

Status of Bank

Commands Allowed in Another Bank

Read

Array

Read

Status

Register

Read CFI

Query

Read

Electronic

Signature

Program,

Buffer

Program

Block

Erase

Program/

Erase

Suspend

Program/

Erase Resume

Idle

Programming

––

–

Erasing

––

–

Program Suspended

––

–

Erase Suspended

––

Table 16: Dual Operations Allowed in Same Bank

Status of Bank

Commands Allowed in Same Bank

Read

Array

Read

Status

Register

Read CFI

Query

Read

Electronic

Signature

Program,

Buffer

Program

Block

Erase

Program/

Erase

Suspend

Program/

Erase Resume

Idle

Programming

–(1)

––

–

Erasing

–(1)

––

–

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| XCF32PFS48C | IC PROM SRL 1.8V 32M 48CSBGA |

| XCR3256XL-7CS280C | IC CPLD 256MCELL 3.3V HP 280CSP |

| XCS10-3VQG100C | IC FPGA 5V C-TEMP 100-VQFP |

| XCV600E-8HQ240C | IC FPGA 1.8V C-TEMP 240-HQFP |

| XCV812E-8FG900C | IC FPGA 1.8V C-TEMP 900-FBGA |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| XCF128XFTG64CES | 制造商:Xilinx 功能描述: |

| XCF12-L4Z1 | 制造商:SAIA - BURGESS ELECTRONICS INC. 功能描述:Catalogue / XCF12-L4Z1 |

| XCF12-S1 | 制造商:SAIA - BURGESS ELECTRONICS INC. 功能描述:Catalogue / XCF12-S1 |

| XCF13-S1 | 制造商:SAIA - BURGESS ELECTRONICS INC. 功能描述:Catalogue / XCF13-S1 |

| XCF16P | 制造商:XILINX 制造商全稱:XILINX 功能描述:Platform Flash In-System Programmable Configuration PROMs |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。