- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄384021 > TMS320AV110 (Texas Instruments, Inc.) MPEG Audio Decoder(MPEG音頻譯碼器) PDF資料下載

參數(shù)資料

| 型號: | TMS320AV110 |

| 廠商: | Texas Instruments, Inc. |

| 英文描述: | MPEG Audio Decoder(MPEG音頻譯碼器) |

| 中文描述: | MPEG音頻解碼器(的MPEG音頻譯碼器) |

| 文件頁數(shù): | 4/38頁 |

| 文件大?。?/td> | 796K |

| 代理商: | TMS320AV110 |

第1頁第2頁第3頁當(dāng)前第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁

TMS320AV110

MPEG AUDIO DECODER

SCSS013C – MAY 1993 – REVISED AUGUST 1995

4

POST OFFICE BOX 655303

DALLAS, TEXAS 75265

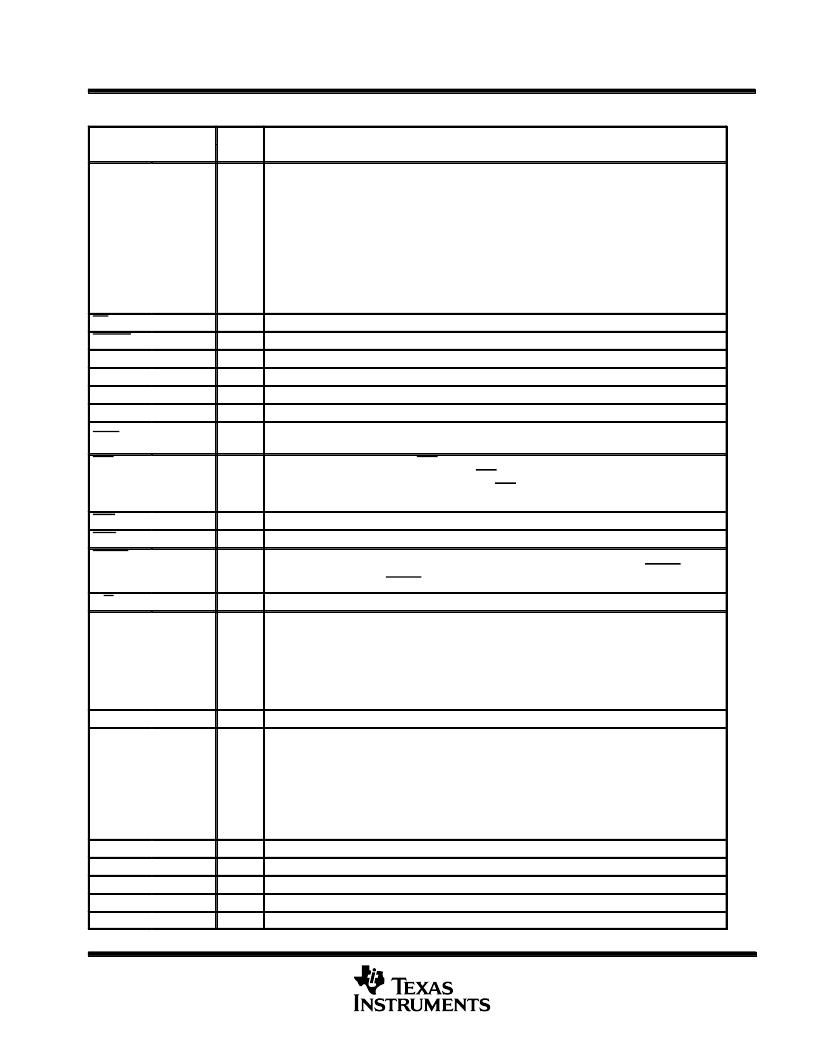

Terminal Functions (continued)

TERMINAL

I/O

DESCRIPTION

NAME

NO.

NC

7, 9, 12,

13, 18, 24,

31, 32, 35,

36, 41, 45,

49, 55, 59,

60, 70, 73,

79, 82, 84,

91, 92, 96,

97, 106,

110, 115,

119, 120

No Connect. These terminals are used for factory testing and should be tied to GND.

OE

44

O

DRAM output enable

OSCEN

6

I

Buffered oscillator (CLKOUT) output enable

OSCIN

3

I

Oscillator input or crystal connection. Asynchronous system clock.

OSCOUT

4

O

Crystal connection (crystal low side)

PCMCLK

14

I

PCM clock input. Used with PCM_DIV register value to generate SCLK and LRCLK.

PCMDATA

20

O

PCM serial data output

PLAY

118

I

Enables the output of decoded audio data. Output of decoded audio data is enabled only if both

this

line and the PLAY register are asserted. Does not affect the output of muted audio (see Table 1).

PTS

11

O

Presentation time stamp output. PTS goes low when the first data word associated with a frame that

contains a PTS is at the PCM output stage. PTS pulses low for every PTS if the PTS interrupt is

not enabled. When the PTS interrupt is enabled, PTS will continue to pulse low if the PTS register

is read after each PTS pulse.

RAS

50

O

DRAM row address strobe

REQ

99

O

Data request

RESET

116

I

Resets the audio decoder. Functionally equivalent to asserting the RESET register except that the

MUTE and PLAY registers are deasserted and the PCM_DIV register is affected. RESET must be

asserted after power up. RESET low disables register accesses.

R/W

95

I

Register read/write select

SADDR6

SADDR5

SADDR4

SADDR3

SADDR2

SADDR1

SADDR0

114

112

111

109

108

107

103

I

Register address bus

SCLK

19

O

Serial PCM output bit clock

SDATA7

SDATA6

SDATA5

SDATA4

SDATA3

SDATA2

SDATA1

SDATA0

77

78

80

81

83

85

86

87

I/O

8-bit parallel data bus for register input/output and audio data input

SIN

88

I

Serial compressed audio data input

TCK

34

I

Test Access Port (TAP) test clock input. Should be tied low for normal operation.

TDI

40

I

TAP test data input

TDO

33

O

TAP test data output

TEST

42

I

Test enable. TEST must be tied low.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| TMS320AV120 | MPEG Audio Decoder(MPEG音頻譯碼器) |

| TMS320AV220 | Video CD MPEG Decoder(視頻CD MPEG編碼器) |

| TMS320AV410 | Digital NTSC/PAL Encoder(數(shù)字NTSC/PAL編碼器) |

| TMS320AV411 | Digital NTSC/PAL Encoder(數(shù)字NTSC/PAL編碼器) |

| TMS320AV420 | Digital NTSC Encoder(數(shù)字NTSC編碼器) |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| TMS320AV120 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Digital Audio Decoder & Support |

| TMS320AV120FN | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Digital Audio Decoder & Support |

| TMS320AV220PCM | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Audio/Video Decoder for MPEG |

| TMS320AV410 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Color Encoder Circuit |

| TMS320AV410PJM | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。