- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄360742 > ICS1531 Triple 8-bit MSPS A/D Converters with Line-Locked Clock Generator PDF資料下載

參數(shù)資料

| 型號(hào): | ICS1531 |

| 英文描述: | Triple 8-bit MSPS A/D Converters with Line-Locked Clock Generator |

| 中文描述: | 三8位MSPS的的A / D轉(zhuǎn)換器與電源同步時(shí)鐘發(fā)生器 |

| 文件頁(yè)數(shù): | 47/76頁(yè) |

| 文件大?。?/td> | 529K |

| 代理商: | ICS1531 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)當(dāng)前第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)第69頁(yè)第70頁(yè)第71頁(yè)第72頁(yè)第73頁(yè)第74頁(yè)第75頁(yè)第76頁(yè)

Chapter 6

Register Set

ICS1531 Rev N 12/1/99

December, 1999

47

Copyright 1999, Integrated Circuit Systems, Inc.

All rights reserved.

ICS1531 Data Sheet - Preliminary

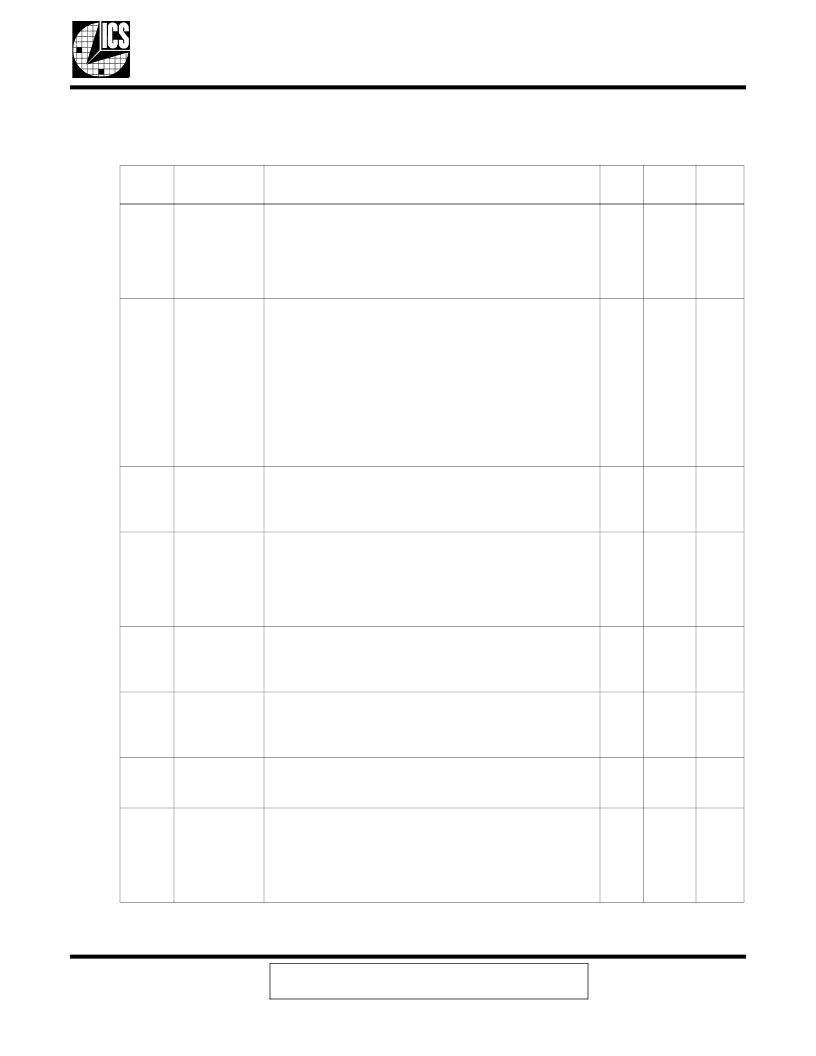

6.5.32

Register 30h: ADC CTRL

The ADC CTRL (Analog-to-Digital Converter Control) Register is used to control the ADC.

Table 6-31.

ADC CTRL Register

Bit

Bit Name

Bit Definition

Ac-

cess

Spec.

Func.

Re-

set

30:7

ADC_OE

Analog-to-Digital Converter (Digital) Outputs Enable.

This bit enables the ADC digital outputs.

0 = The ADC digital outputs are disabled.

(The ICS1531 output pads are high-impedance.)

1 = The ADC digital outputs are enabled.

(The polarity is controlled by Reg 30:5.)

R/W

–

0

30:6

ADC_Sel

Analog-to-Digital Converter (Capture) Select.

This bit selects a mode for the ADC.

0 =

– The clock rate is 2 pixels per clock (half-rate clock).

– Both the ‘A’ and ‘B’ channels each provide 24-bit pixels

(48 bits total).

1 =

– The clock rate is 1 pixel per clock (full-rate clock).

– The ‘A’ channel provides 24-bit pixels (24 bits total).

– The ‘B’ channel is driven either high or low, depending

on the value of Reg 30:5 (ADC_INV).

R/W

–

0

30:5

ADC_Inv

Analog-to-Digital Converter (Output) Invert (Disable).

This bit disables the inversion of the ADC outputs.

0 = The ADC outputs are inverted.

1 = The ADC outputs are not inverted (default).

R/W

–

1

30:4

Force_ADC

Force Analog-to-Digital Converter (Outputs).

This bit forces to ‘off’ all output buffers for the ADC pin.

0 = Normal operation

1 = Force all ADC output buffers low or high as follows:

– Reg 30:5 = 0 to force buffers low

– Reg 30:5 = 1 to force buffers high

R/W

–

0

30:3

CLAMP_Pol

Clamp Polarity.

This bit selects the polarity of the signal to a clamp.

0 = The polarity of the signal to a clamp is positive.

1 = The polarity of the signal to a clamp is negative.

R/W

–

0

30:2

CLAMP_Sel

Clamp (Source) Select.

This bit selects the source of the signal to a clamp.

0 = The source of the signal is internally generated.

1 = The source of the signal is from the CLAMP pin.

R/W

–

0

30:1

VA_Disable

Video Amplifier Disable.

0 = Video amplifier is enabled (default).

1 = Video amplifier is disabled to conserve power.

–

–

0

30:0

FA_Disable

Fine Adjust Disable.

0 = The DACs are enabled and they drive the VRTR,

VRTG, and VRTB pins internally.

1 = The DACs are disabled and the VRTR, VRTG, and

VRTB pins must be driven externally with ADC top

reference voltage.

R/W

–

0

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| ICS1560M-001 | Video/Graphics Clock Generator |

| ICS1560M-003 | Video/Graphics Clock Generator |

| ICS1560N-001 | Video/Graphics Clock Generator |

| ICS1560N-003 | Video/Graphics Clock Generator |

| ICS1561AM-706 | Video/Graphics Clock Generator |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| ICS1532 | 制造商:IDT 制造商全稱(chēng):Integrated Device Technology 功能描述:110 MHZ TRIPLE 8-BIT ADC WITH CLOCK GENERATOR |

| ICS1560M-001 | 制造商:未知廠家 制造商全稱(chēng):未知廠家 功能描述:Video/Graphics Clock Generator |

| ICS1560M-003 | 制造商:未知廠家 制造商全稱(chēng):未知廠家 功能描述:Video/Graphics Clock Generator |

| ICS1560N-001 | 制造商:未知廠家 制造商全稱(chēng):未知廠家 功能描述:Video/Graphics Clock Generator |

| ICS1560N-003 | 制造商:未知廠家 制造商全稱(chēng):未知廠家 功能描述:Video/Graphics Clock Generator |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。