- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄370584 > HIP8112A (Harris Corporation) NTSC/PAL Video Decoder PDF資料下載

參數(shù)資料

| 型號(hào): | HIP8112A |

| 廠商: | Harris Corporation |

| 英文描述: | NTSC/PAL Video Decoder |

| 中文描述: | NTSC / PAL視頻解碼器 |

| 文件頁(yè)數(shù): | 5/40頁(yè) |

| 文件大小: | 719K |

| 代理商: | HIP8112A |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)當(dāng)前第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)

4-5

Introduction

The HMP8112A is designed to decode baseband composite

or s-video NTSC and PAL signals, and convert them to either

digital YCbCr or RGB data.

The digital PLLs are designed to synchronize to all NTSC

and PAL standards. A chroma PLL is used to maintain

chroma lock for demodulation of the color information; a line-

locked PLL is used to maintain vertical spatial alignment.

The PLLs are designed to maintain lock even in the event of

VCR headswitches.

The HMP8112A contains two 8-bit A/D converters and an

I

2

C port for programming internal registers

Analog Video Inputs

The HMP8112A supports either three composite or two

composite and one S-Video input.

Three analog video inputs (LIN0, LIN1, LIN2) are used to

select which one of three composite video sources are to be

decoded. To support S-video applications, the Y channel

drives the LIN2 analog input, and the C channel drives the

CIN analog input.

The analog inputs must be AC-coupled to the video signals,

as shown in the Applications section.

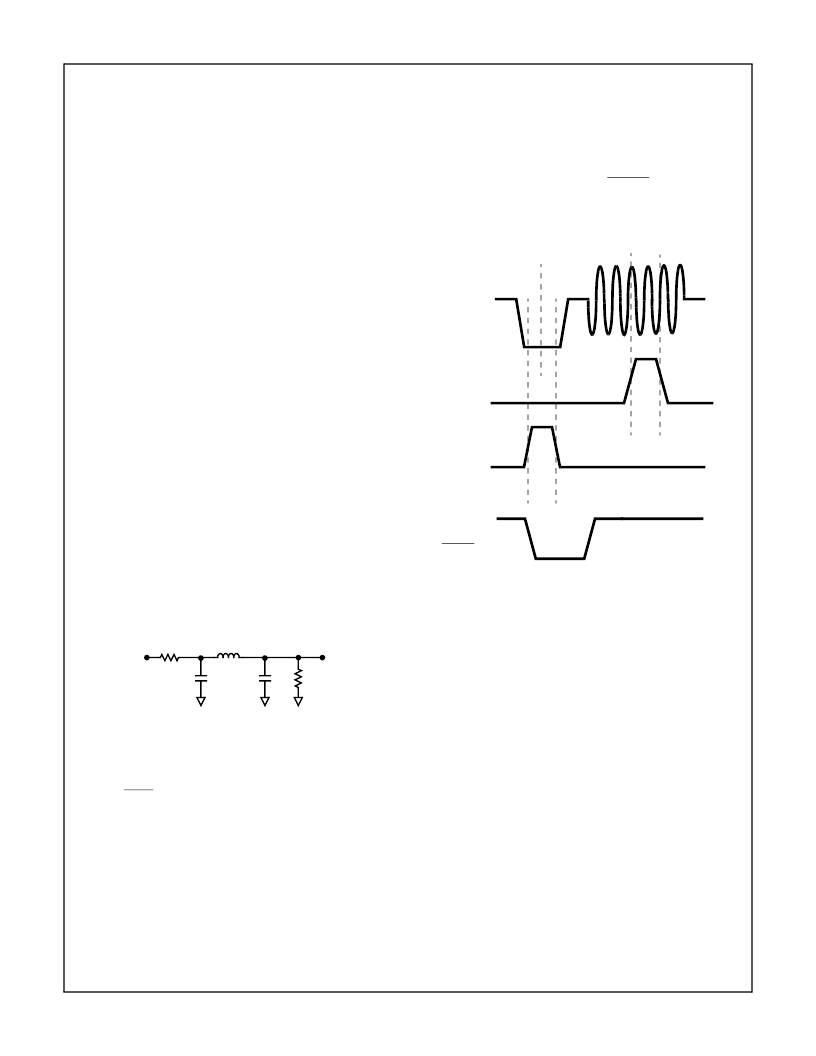

Anti-Aliasing Filter

An external anti-alias filter is required to achieve optimum

performance and prevent high frequency components from

being aliased back into the video image.

For the LIN0-2 inputs, a single filter is connected to L_OUT

and L_ADIN. For CIN the anti-aliasing filter should be con-

nected to the CIN input. A recommended filter is shown

below in Figure 1.

Luminance AGC And DC RESTORE Circuits

After a

RESET

, a change of the video standard, or a PLL

Chrominance Subcarrier Ratio Register load, the decoder

enters Acquisition Mode by attempting to lock to a new video

source. During this mode, the HAGC and DC RESTORE cir-

cuits perform continuous gain and bias adjustments until the

PLL is LOCKED onto the video signal. Once LOCKED, the

HAGC and DC RESTORE functions are performed during

programmable window periods for each horizontal video line.

The digital PLL zeroes a 10-bit pixel clock counter during

each horizontal sync tip and increments the count for each

pixel of the entire video line. The AGC amplifier attenuates or

amplifies the analog video signal during the horizontal sync

tip to maintain an average ADC code of 0. The DC

RESTORE circuit clamps the video signal during the back

porch to maintain an average ADC code of 64. Reference

Figure 2 for timing information and Table 5 for the recom-

mended register values to use for different video standards.

The START and END times of the HSYNC output are also

programmable and can be used as a reference for confirm-

ing proper HAGC and DC RESTORE timing.

White Peak Enable

The white peak enable input, (WPE) enables or disables the

white peak control of the luminance input. If enabled, the

AGC will reduce the gain of the video amplifier when the dig-

ital outputs exceed code 248 to prevent over-ranging the

A/D. If disabled, the AGC operates normally, keeping the hor-

izontal sync tip at code 0 and allowing the A/D’s range to go

to 255 at the maximum peak input.

Chrominance Input

The chrominance amplifier gain control is manually set by a

voltage applied to the GAIN_CNTL pin. Refer to Figure 3

below for gain characteristics. The chrominance channel

also has a digital AGC which can drive the color reference

burst to a nominal +-20 IRE. This function is enabled by

default on reset, but can be disabled using the Video Input

Control register. The chrominance input is clamped during

the DC RESTORE window to maintain an average ADC

code of 128.

FIGURE 1. RECOMMENDED ANTI-ALIASING FILTER

R1

332

R2

4.02K

C2

82pF

L1

8.2

μ

H

C1

33pF

FIGURE 2. DC RESTORE AND HAGC TIMING

VIDEO INPUT

HAGC

DC RESTORE

START

TIME

END

TIME

START

TIME

END

TIME

0

HSYNC

HSYNC

START

TIME

END

TIME

HMP8112A

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| HIR19-21C | Technical Data Sheet 0.8mm Height Flat Top Infrared LED |

| HIR19-L11 | Technical Data Sheet 0.8mm Height Flat Top Infrared LED |

| HIR204C | 3mm Infrared LED, T-1 |

| HIR | 5mm Infrared LED, T-1 3/4 |

| HIR333 | 5mm Infrared LED, T-1 3/4 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| HIP-8V | 制造商:Belden Inc 功能描述:SPLITTER 8 WAY |

| HIP9010 | 制造商:INTERSIL 制造商全稱(chēng):Intersil Corporation 功能描述:Engine Knock Signal Processor |

| HIP9010AB | 制造商:Intersil Corporation 功能描述: |

| HIP9011 | 制造商:INTERSIL 制造商全稱(chēng):Intersil Corporation 功能描述:Engine Knock Signal Processor |

| HIP9011_06 | 制造商:INTERSIL 制造商全稱(chēng):Intersil Corporation 功能描述:Engine Knock Signal Processor |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。