- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄384021 > TMS320AV220 (Texas Instruments, Inc.) Video CD MPEG Decoder(視頻CD MPEG編碼器) PDF資料下載

參數(shù)資料

| 型號: | TMS320AV220 |

| 廠商: | Texas Instruments, Inc. |

| 英文描述: | Video CD MPEG Decoder(視頻CD MPEG編碼器) |

| 中文描述: | 視頻CD MPEG解碼器(視頻光盤的MPEG編碼器) |

| 文件頁數(shù): | 13/31頁 |

| 文件大小: | 612K |

| 代理商: | TMS320AV220 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁當(dāng)前第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁

TMS320AV220

VIDEO CD MPEG DECODER

SCSS016A – JUNE 1994 – REVISED JANUARY 1996

13

POST OFFICE BOX 655303

DALLAS, TEXAS 75265

STILL_MODE, still-picture-display mode, 1:0 (2422h) (continued)

This register controls the display of normal-resolution still pictures. When bit 1 is set to 1, the input buffer is

cleared, audio synchronization (PTS comparison) is disabled but the audio is not muted, and the first I-frame

found is displayed. The ’AV220 enters a pause mode until bit 0 is set to 1 by a host, indicating a request to display

the next I-frame. This bit is then cleared by the device. To return to normal play mode, bit 1 must be cleared.

The user must not set the FAST and STILL_MODE registers to 1 at the same time.

STREAM_EN, stream enable (2420h)

0 = Normal operation

1 = Enables streaming data write from CDATA to the 4M-bit DRAM, starting at address 0. The data should

not be sent until 600 ns after the write to this register is completed. This register must be cleared after the

last data is written.

This register controls direct, high-speed data write from the CD-ROM decoder to the video-buffer DRAM. When

set to 1, the device resets itself. The data on the compressed-data input is written into consecutive locations

in the DRAM starting at address 0. Direct write stops when either this register is cleared by the host or the

memory is full. The addresses do not roll over. A memory-full interrupt is also generated (if enabled). After the

STREAM_EN bit returns to 0, the written data can be randomly accessed via the host interface. Microcode and

working buffers are overwritten during this operation, and high-speed memory writes must be followed by a reset

after the data is processed by the host.

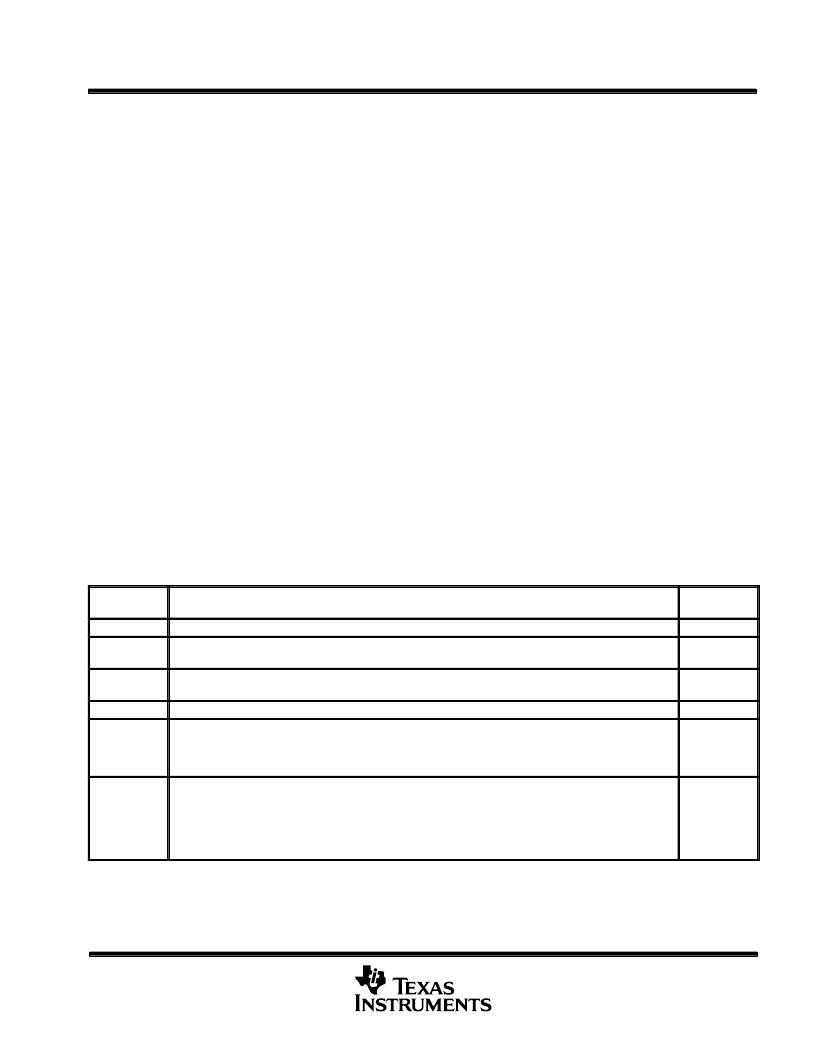

SYNC_CTL, synchronization control (242Bh)

This register allows control of the incoming MPEG-stream time stamps. SYNC_CTL allows modification of the

interval at which incoming SCR values (extracted from the incoming MPEG stream) are used to update the

internal 90-kHz counter used for synchronization. This register also allows both audio and video synchronization

to be disabled. The default value works well for most applications. For problem CDs, this register may need to

be set to 34h or some other value. Video-only systems may require synchronization to be disabled to achieve

the proper play rate. The SYNC_CTL register is defined as follows:

BIT NO.

FUNCTION

DEFAULT

VALUE

7:6

Don’t care

01

5

Audio-synchronization enable. When set enables audio synchronization; when cleared audio synchronization

is disabled (PTS values are not sent to the ’AV120).

1

4

Video-synchronization enable. When set enables video synchronization; when cleared video synchronization

is disabled (PTS values are not sent to the video core).

1

3

Don’t care

1

2

1SCR – When set, the ’AV220 uses only the first SCR time stamp after a change in the PLAY mode (e.g., play

to pause, still to play, etc.). SCRs that occur later in the MPEG stream are ignored and do not update the

internal 90-kHz counter. Bits 1:0 have no affect when bit 2 is set. When bit 2 is cleared, bits 1:0 determine the

SCR update interval.

0

1:0

SCR update control bits. Controls the rate at which incoming SCRs update the internal 90-kHz counter after

the 1st SCR is received by the ’AV220.

00 : 720 mS (min) between SCR updates

01 : 360 mS (min) between SCR updates

10 : 180 mS (min) between SCR updates

11 : 90 mS (min) between SCR updates

00

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| TMS320AV410 | Digital NTSC/PAL Encoder(數(shù)字NTSC/PAL編碼器) |

| TMS320AV411 | Digital NTSC/PAL Encoder(數(shù)字NTSC/PAL編碼器) |

| TMS320AV420 | Digital NTSC Encoder(數(shù)字NTSC編碼器) |

| TMS320C6424_1 | Fixed-Point Digital Signal Processor |

| TMS320C6455ZTZ | Fixed-Point Digital Signal Processor |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| TMS320AV220PCM | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Audio/Video Decoder for MPEG |

| TMS320AV410 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Color Encoder Circuit |

| TMS320AV410PJM | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| TMS320AV411 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Color Encoder Circuit |

| TMS320AV411PJM | 制造商:Rochester Electronics LLC 功能描述:- Bulk 制造商:Texas Instruments 功能描述: |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。