- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄375249 > AD9865CHIPS (ANALOG DEVICES INC) Broadband Modem Mixed-Signal Front End PDF資料下載

參數(shù)資料

| 型號: | AD9865CHIPS |

| 廠商: | ANALOG DEVICES INC |

| 元件分類: | 通信及網(wǎng)絡 |

| 英文描述: | Broadband Modem Mixed-Signal Front End |

| 中文描述: | SPECIALTY TELECOM CIRCUIT, UUC |

| 封裝: | DIE |

| 文件頁數(shù): | 19/48頁 |

| 文件大?。?/td> | 1672K |

| 代理商: | AD9865CHIPS |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁當前第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁

AD9865

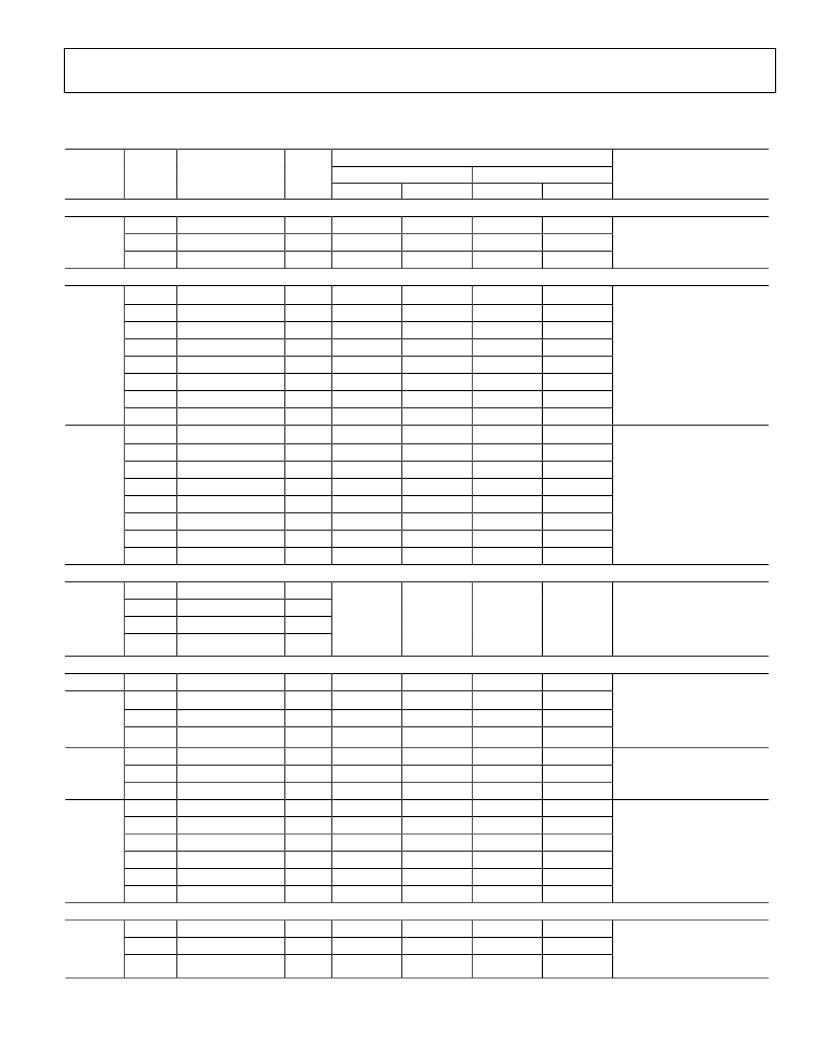

SERIAL PORT

Table 10. SPI Register Mapping

Rev. A | Page 19 of 48

Power-Up Default Value

MODE = 0 (Half-Duplex)

CONFIG = 0

MODE = 1 (Full-Duplex)

CONFIG = 0

Address

(Hex)

1

SPI PORT CONFIGURATION AND SOFTWARE RESET

0x00

(7)

4-Wire SPI

(6)

LSB First

(5)

S/W Reset

POWER CONTROL REGISTERS (via PWR_DWN pin)

0x01

(7)

Clock Syn.

(6)

TxDAC/IAMP

(5)

Tx Digital

(4)

REF

(3)

ADC CML

(2)

ADC

(1)

PGA Bias

(0)

RxPGA

0x02

(7)

CLK Syn.

(6)

TxDAC/IAMP

(5)

Tx Digital

(4)

REF

(3)

ADC CML

(2)

ADC

(1)

PGA Bias

(0)

RxPGA

HALF-DUPLEX POWER CONTROL

0x03

(7:3)

Tx OFF Delay

(2)

Rx _TXEN

(1)

Tx PWRDN

(0)

Rx PWRDN

Bit

Break-

down

Description

Width

CONFIG = 1

CONFIG = 1

Comments

1

1

1

0

0

0

0

0

0

0

0

0

0

0

0

Default SPI configuration is

3-wire, MSB first.

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

0

0

0

0

0

0

0

0

0

1

1

1

1

1

1

1

0

0

0

0

0

0

0

0

0

1

1

1

1

1

1

1

0

0

0

0

0

0

0

0

0

1

1

1

1

1

1

1

0

0

0

0

0

0

0

0

1*

1

1

1

1

1

1

1

PWR_DWN = 0.

Default setting is for all

blocks powered on.

PWR_DWN = 1.

Default setting* is for all

functional blocks powered

down except PLL.

*MODE = CONFIG = 1.

Setting has PLL powered

down with OSCIN input

routed to RXCLK output.

5

1

1

1

0xFF

0xFF

N/A

N/A

Default setting is for TXEN

input to control power

on/off of Tx/Rx path.

Tx driver delayed by 31

1/f

DATA

clock cycles.

PLL CLOCK MULTIPLIER/SYNTHESIZER CONTROL

0x04

(5)

Duty Cycle Enable

(4)

f

ADC

from PLL

(3:2)

PLL Divide-N

(1:0)

PLL Multiplier-M

0x05

(2)

OSCIN to RXCLK

(1)

Invert RXCLK

(0)

Disabled RXCLK

0x06

(7:6)

CLKOUT2 Divide

(5)

CLKOUT2 Invert

(4)

CLKOUT2 Disable

(3:2)

CLKOUT1 Divide

(1)

CLKOUT1 Invert

(0)

CLKOUT1 Disable

Rx PATH CONTROL

0x07

(5)

Initiate Offset Cal.

(4)

Rx Low Power

(0)

Rx Filter ON

1

1

2

2

0

0

00

01

0

0

00

10*

0

0

00

01

0

0

00

01

Default setting is Duty Cycle

Restore disabled, ADC CLK

from OSCIN input, and PLL

multiplier × 2 setting.

*PLL multiplier × 4 setting.

Full-duplex RXCLK normally

at nibble rate.

*Exception on power-up.

1

1

1

2

1

1

2

1

1

0

0

0

01

0

0

01

0

0

0

0

0

01

0

0

01

0

0

0

0

0

01

0

0

01

0

0

1*

0

0

01

0

1*

01

0

1*

Default setting is CLKOUT2

and CLKOUT1 enabled with

divide-by-2.

*CLKOUT1 and CLKOUT2

disabled.

1

1

1

0

0

1

0

1*

1

0

0

1

0

1*

1

Default setting has LPF ON

and Rx path at nominal

power bias setting.

*Rx path to low power.

相關PDF資料 |

PDF描述 |

|---|---|

| AD9887 | Dual Interface for Flat Panel Displays |

| AD9888 | 100/140/170/205 MSPS Analog Flat Panel Interface |

| AD9888KS-100 | 100/140/170/205 MSPS Analog Flat Panel Interface |

| AD9888KS-140 | TRI N PLUG F 2-13 |

| AD9888KS-170 | TRI N RECP M FLG 2-13 |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| AD9865-EB | 制造商:Analog Devices 功能描述:MODEM, BROADBAND MODEM MIXED SGNL FRONT END - Bulk |

| AD9866 | 制造商:AD 制造商全稱:Analog Devices 功能描述:Broadband Modem Mixed-Signal Front End |

| AD9866BCP | 制造商:Analog Devices 功能描述:Mixed Signal Front End 64-Pin LFCSP EP 制造商:Analog Devices 功能描述:12BIT MIXED SIGNAL CONVERTER 9866 |

| AD9866BCPRL | 制造商:Analog Devices 功能描述:Mixed Signal Front End 64-Pin LFCSP EP T/R |

| AD9866BCPZ | 功能描述:IC PROCESSOR FRONT END 64LFCSP RoHS:是 類別:RF/IF 和 RFID >> RF 前端 (LNA + PA) 系列:- 產品培訓模塊:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 標準包裝:250 系列:- RF 型:GPS 頻率:1575.42MHz 特點:- 封裝/外殼:48-TQFP 裸露焊盤 供應商設備封裝:48-TQFP 裸露焊盤(7x7) 包裝:托盤 |

發(fā)布緊急采購,3分鐘左右您將得到回復。