- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄384042 > UPD30181AYF1-131-GA3-A (NEC Corp.) 64-/32-BIT MICROPROCESSOR PDF資料下載

參數(shù)資料

| 型號(hào): | UPD30181AYF1-131-GA3-A |

| 廠商: | NEC Corp. |

| 英文描述: | 64-/32-BIT MICROPROCESSOR |

| 中文描述: | 64-/32-BIT微處理器 |

| 文件頁數(shù): | 12/72頁 |

| 文件大?。?/td> | 447K |

| 代理商: | UPD30181AYF1-131-GA3-A |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁當(dāng)前第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁

Data Sheet U16277EJ1V0DS

12

μ

PD30181A, 30181AY

(3/3)

Signal Name

I/O

Function

Alternate Function

SYSDIR

Note

O

Data bus isolation buffer direction control

This signal is valid only when accessing devices other than SDRAM or

SyncFlash memory devices. The signal is at high level during read

cycles and at low level during write cycles.

–

SYSEN#

Note

O

Enables data bus isolation buffer connection

This signal is set to high level during SDRAM and SyncFlash memory

cycles and is at low level when accessing any other devices.

–

DRQ(1:0)#

I

DMA service request signal

The DRQ(1:0)# signals are sampled at the rising edge of TClock. Be

sure to hold this signal at active level until a DMA request is

acknowledged. Set this signal as inactive when not using the DRQ(1:0)#

signals.

–

DAK(1:0)#

O

Enables DMA service request

This signal goes to active level when access to the target device occurs

via DMA transfer.

–

TC(1:0)#

I/O

DMA transfer completion signal (open drain)

This signal is driven at active level when a DMA transfer is completed.

During a transfer, this signal operates as a DMA stop request input

signal.

GPIO(53:52)

NMI#

I

Non-maskable interrupt input

This is an interrupt request signal that cannot be masked in relation to the

CPU core. When the V

R

4181A starts normally and the MPOWER signal

is at high level, input from the NMI# pin is connected to the CPU core via

the ICU. While the MPOWER signal is at low level, input to the NMI# pin

is monitored by the PMU as a source of NMI shutdowns.

–

Note

The SYSEN# and SYSDIR signals are buffer control signals used to isolate the SDRAM and SyncFlash

memory buses from other low-speed device buses. Isolating high-speed memory access paths from other

devices reduces the load on the system bus between the V

R

4181A and the SDRAM or SyncFlash

memory. When using the system bus isolation buffer, the correspondence between the SYSEN# and

SYSDIR signals and the data bus isolation status is as shown below.

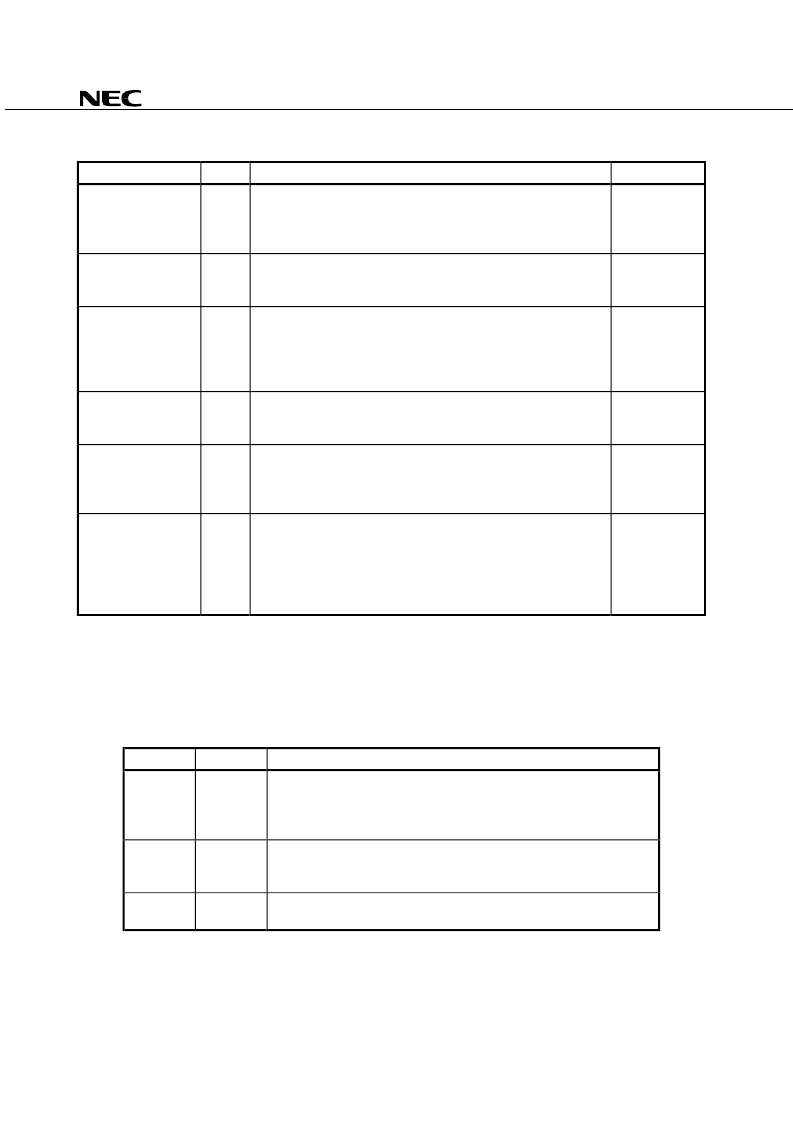

SYSEN#

SYSDIR

Bus Operation

0

0

Enables connection via data bus isolation buffer

Write cycle for ROM, flash memory, SRAM, ISA device, CompactFlash/PC

Card, or other general-purpose device

Hibernate mode

0

1

Enables connection via data bus isolation buffer

Read cycle for ROM, flash memory, SRAM, ISA device, CompactFlash/PC

Card, or general-purpose device

1

0

Disables connection via data bus isolation buffer

Read/write cycle for SDRAM or SyncFlash memory

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| UPD30181GM-66-8ED | 64-/32-Bit Microprocessor |

| UPD3570 | UPD3570 2560-BIT CCD LINEAR IMAGE SENSOR |

| UPD3570D | UPD3570 2560-BIT CCD LINEAR IMAGE SENSOR |

| UPD3571 | 5000 BIT CCD LINEAR IMAGE SENSOR |

| UPD3571D | 5000 BIT CCD LINEAR IMAGE SENSOR |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| UPD30181GM-66-8ED | 制造商:NEC 制造商全稱:NEC 功能描述:64-/32-Bit Microprocessor |

| UPD30200 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:VR4300(TM).VR4305(TM).VR4310(TM) User's Manual | User's Manual[08/2000] |

| UPD30200GD-100MBB | 制造商:NEC Electronics Corporation 功能描述: |

| UPD30200GD-100-MBB | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:64-Bit Microprocessor |

| UPD30200GD-133-MBB | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:64-Bit Microprocessor |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。