- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄98303 > TSC2302IRGZRG4 (TEXAS INSTRUMENTS INC) SPECIALTY CONSUMER CIRCUIT, PQCC48 PDF資料下載

參數(shù)資料

| 型號(hào): | TSC2302IRGZRG4 |

| 廠商: | TEXAS INSTRUMENTS INC |

| 元件分類: | 消費(fèi)家電 |

| 英文描述: | SPECIALTY CONSUMER CIRCUIT, PQCC48 |

| 封裝: | GREEN, PLASTIC, VQFN-48 |

| 文件頁數(shù): | 70/85頁 |

| 文件大小: | 1483K |

| 代理商: | TSC2302IRGZRG4 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁當(dāng)前第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁

www.ti.com

TSC2302

SLAS394 – JULY 2003

Bit [15:3] — RESERVED

These bits are reserved, and should be written to a default value.

Bit 2 — MONS

Mono Select. This bit determines the position of the mono multiplexer. This multiplexer allows either the left

channel ADC Input or the mono mix of the stereo headphone outputs to be played out of the differential mono

output (MONO+/-).

Table 38. Mono Select

MONS

DESCRIPTION

0

Mono output comes from left ADC input (default).

1

Mono output comes from mono mix of headphone outputs.

Bit 1 — SSRTE

Volume Soft-stepping Rate Select. This bit selects the speed of the soft-stepping function of the TSC2302

volume controls. At normal speed, the actual volume is updated approximately once every 20 s. At half speed,

the actual volume is updated approximately once every 40 s.

Table 39. Volume Soft-Stepping Rate Select

SSRTE

DESCRIPTION

0

Normal step rate used (default).

1

Half step rate used.

Bit 0 — SSTEP

Soft-step Flag. This read-only bit indicates that the TSC2302 volume control soft-stepping is completed.

Table 40. Soft-Step Flag

SSTEP

DESCRIPTION

0

Soft-stepping is not complete

1

Soft-stepping is complete (default)

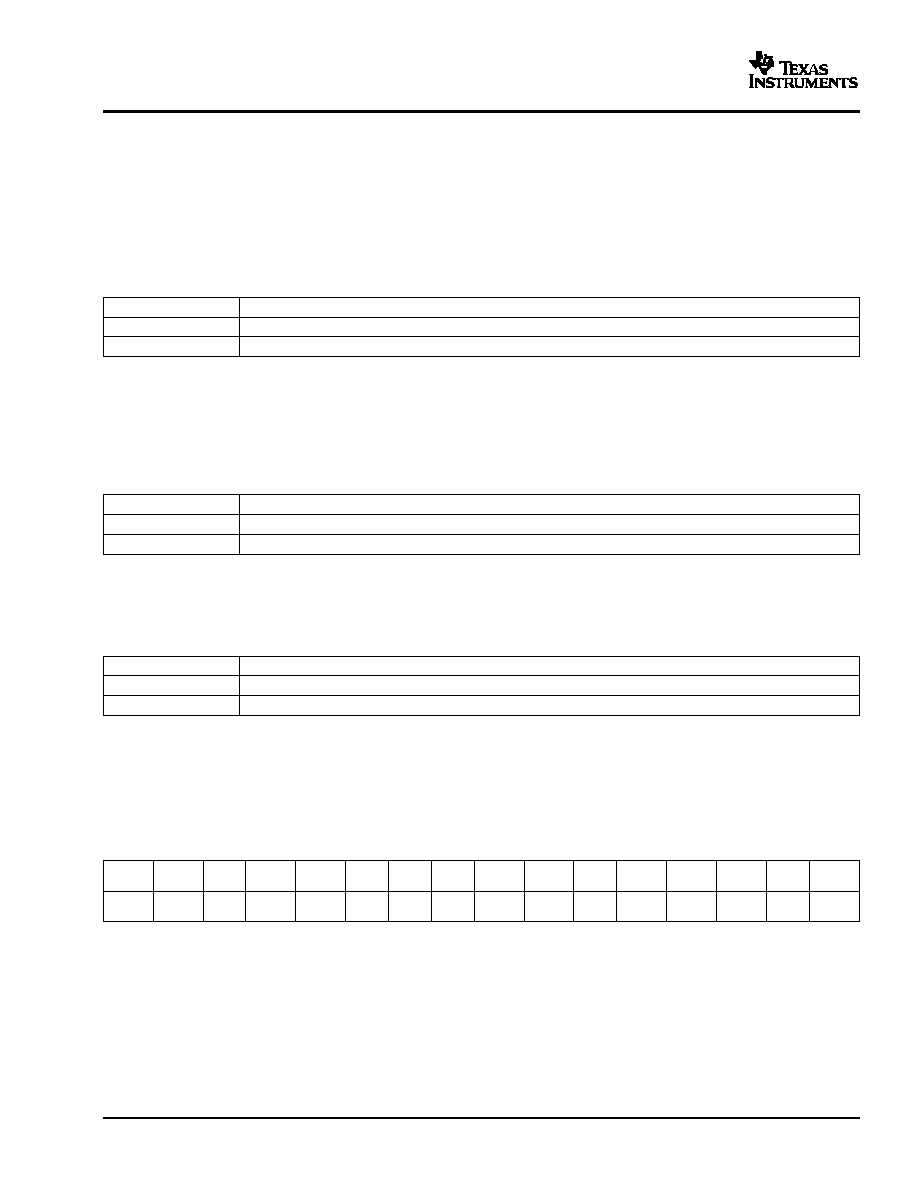

AUDIO POWER CONTROL REGISTER (Page 2, Address 05H)

The audio power / miscellaneous control register of the TSC2302 controls the powering down of various audio

blocks of the TSC2302. The default state of the TSC2302 has all audio blocks powered down. Before using any

of the audio blocks, they must be powered up by writing to this register. This register also controls the crystal

oscillator clock and buffer, the bass-boost filter, and the de-emphasis filter.

The audio power / miscellaneous control register is formatted as follows:

BIT 15

BIT 14

BIT 13

BIT 12

BIT 11

BIT 10

BIT 9

BIT 8

BIT 7

BIT 6

BIT 5

BIT 4

BIT 3

BIT 2

BIT 1

BIT 0

MSB

LSB

APD

AVPD

ABPD

HAPD

MOPD

DAPD

ADPD

PDSTS

MIBPD

OSCC

BCKC

SMPD

OTSYN

BASS

DEEMP

L

R

For bits 15 through 8 of this register, writing a 1 to a selected bit powers down the affected section, writing a 0

powers up the section.

Bit 15 — APD

Audio Power Down. This bit powers down the entire audio section if set, regardless of the settings of the other

bits in this register. When this bit is cleared, the individual sections of the audio codec still need to be powered

up individually. The settings of the other bits in the register are retained when this bit is set and cleared. The

default is 1 (powered down).

72

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| TSDC4872IJT | 1 W, 1 CHANNEL, AUDIO AMPLIFIER, PBGA8 |

| TS4872IJT | 1 W, 1 CHANNEL, AUDIO AMPLIFIER, PBGA8 |

| TSH103ID | 3 CHANNEL, VIDEO AMPLIFIER, PDSO8 |

| TSH103IDT | 3 CHANNEL, VIDEO AMPLIFIER, PDSO8 |

| TSH120ICT | SPECIALTY CONSUMER CIRCUIT, PDSO6 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| TSC2303IZQZ | 制造商:Texas Instruments 功能描述: |

| TSC2303IZQZR | 制造商:Texas Instruments 功能描述: |

| TSC236 | 制造商:TSC 制造商全稱:Taiwan Semiconductor Company, Ltd 功能描述:High Voltage NPN Transistor |

| TSC236CIC0 | 制造商:TSC 制造商全稱:Taiwan Semiconductor Company, Ltd 功能描述:High Voltage NPN Transistor |

| TSC236CZ C0 | 功能描述:兩極晶體管 - BJT High voltage NPN Transistor RoHS:否 制造商:STMicroelectronics 配置: 晶體管極性:PNP 集電極—基極電壓 VCBO: 集電極—發(fā)射極最大電壓 VCEO:- 40 V 發(fā)射極 - 基極電壓 VEBO:- 6 V 集電極—射極飽和電壓: 最大直流電集電極電流: 增益帶寬產(chǎn)品fT: 直流集電極/Base Gain hfe Min:100 A 最大工作溫度: 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:PowerFLAT 2 x 2 |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。