- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄384031 > TSB14C01AM (Texas Instruments, Inc.) 5-V IEEE 1394-1995 BACKPLANE TRANSCEIVER/ARBITER PDF資料下載

參數(shù)資料

| 型號: | TSB14C01AM |

| 廠商: | Texas Instruments, Inc. |

| 英文描述: | 5-V IEEE 1394-1995 BACKPLANE TRANSCEIVER/ARBITER |

| 中文描述: | 5V的電機及電子學(xué)工程師聯(lián)合會1394-1995背板收發(fā)器/仲裁者 |

| 文件頁數(shù): | 24/31頁 |

| 文件大?。?/td> | 424K |

| 代理商: | TSB14C01AM |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁當前第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁

TSB14C01A, TSB14C01AI, TSB14C01AM

5-V IEEE 1394-1995 BACKPLANE TRANSCEIVER/ARBITER

SGLS107A – FEBRUARY 1999 – REVISED NOVEMBER 1999

24

POST OFFICE BOX 655303

DALLAS, TEXAS 75265

PRINCIPLES OF OPERATION

fairness intervals (continued)

Fairness Interval (N)

a

arb

a

arb

data

a

arb

a

arb

data

a

data

arb

Owner A

Owner B

Owner M

Fairness

Interval (N –1)

Fairness

Interval (N +1)

Subaction

Arbitration

Reset Gap

Subaction Gaps

Arbitration

Reset Gap

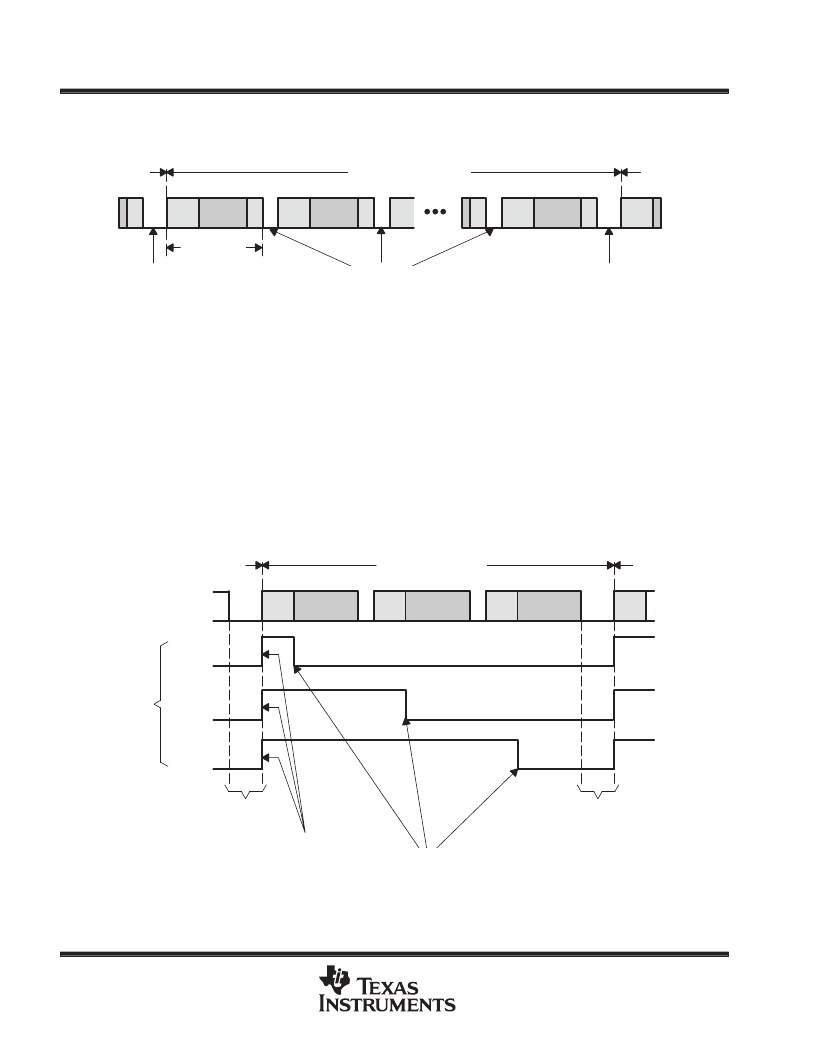

Figure 11. Fairness Interval

The implementation of the fair arbitration protocol is defined in terms of these fairness intervals as discussed

in the following paragraphs.

fair arbitration

When using this arbitration class, an active node can send an asynchronous packet only once each fairness

interval. Once a subaction gap is detected, a node can begin arbitration when its arbitration_enable signal is

set. The arbitration_enable signal is set at the beginning of the fairness interval and is cleared when the node

successfully accesses the bus through fair arbitration. This disables further fair arbitration attempts by that node

for the remainder of the fairness interval. In the absence of urgent nodes, a fairness interval ends once all of

the nodes attempting fair arbitration have successfully accessed the bus. At this time, all of the fair nodes have

their arbitration_enable signals reset and cannot arbitrate for the bus. The bus remains idle until an arbitration

reset gap occurs. Once this happens, the next fairness interval begins. All of the nodes set their

arbitration_enable signal and can begin to arbitrate for the bus. This process is illustrated in Figure 12.

Fairness Interval (N)

arb

arb

node A

arb

Fairness

Interval (N –1)

Fairness

Interval (N +1)

Cleared When Node Wins Arbitration

node B

arb

node C

Arbitration

Reset Gap

Arbitration

Reset Gap

Set at Arbitration Reset Gap

Node A

Node B

Node C

Arbitration

Enable

NOTE A: The arbitration number of A > B > C.

Figure 12. Fair Arbitration Timing

Note that a node sending a concatenated subaction does not reset its arb_enable bit.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| TSSOP-56 | Fairchild Semiconductor Product Package Material Disclosure |

| TSSOP-8PIN | Package Dimensions |

| TSWC01622 | SONET/SDH/PDH/ATM Clock Synthesizer and Protection Switch(SONET/SDH/PDH/ATM 時鐘合成器和保護開關(guān)) |

| TTB28F400BV-B60 | LAMP FILAMENT 14V 16MM |

| TTB28F200CV-B60 | 2-MBIT SmartVoltage BOOT BLOCK FLASH MEMORY FAMILY |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| TSB14C01AMHV | 制造商:TI 制造商全稱:Texas Instruments 功能描述:5-V IEEE 1394-1995 BACKPLANE TRANSCEIVER/ARBITER |

| TSB14C01APM | 功能描述:1394 接口集成電路 5V 50/100Mbps Backplane PLC RoHS:否 制造商:Texas Instruments 類型:Link Layer Controller 工作電源電壓: 封裝 / 箱體:LQFP 封裝:Tray |

| TSB14C01APMG4 | 功能描述:1394 接口集成電路 5V 50/100Mbps Backplane PLC RoHS:否 制造商:Texas Instruments 類型:Link Layer Controller 工作電源電壓: 封裝 / 箱體:LQFP 封裝:Tray |

| TSB14C01APMR | 功能描述:1394 接口集成電路 50/100Mbps BACKPLANE Phy Layer Cntrlr RoHS:否 制造商:Texas Instruments 類型:Link Layer Controller 工作電源電壓: 封裝 / 箱體:LQFP 封裝:Tray |

| TSB14C01APMRG4 | 功能描述:1394 接口集成電路 5V 1Port 50/100Mbps BP Phy Layer Cntrlr RoHS:否 制造商:Texas Instruments 類型:Link Layer Controller 工作電源電壓: 封裝 / 箱體:LQFP 封裝:Tray |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。