- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄98068 > S1C63567F0A0100 MICROCONTROLLER, PQFP144 PDF資料下載

參數(shù)資料

| 型號: | S1C63567F0A0100 |

| 元件分類: | 微控制器/微處理器 |

| 英文描述: | MICROCONTROLLER, PQFP144 |

| 封裝: | PLASTIC, QFP-144 |

| 文件頁數(shù): | 106/172頁 |

| 文件大小: | 1349K |

| 代理商: | S1C63567F0A0100 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁當前第106頁第107頁第108頁第109頁第110頁第111頁第112頁第113頁第114頁第115頁第116頁第117頁第118頁第119頁第120頁第121頁第122頁第123頁第124頁第125頁第126頁第127頁第128頁第129頁第130頁第131頁第132頁第133頁第134頁第135頁第136頁第137頁第138頁第139頁第140頁第141頁第142頁第143頁第144頁第145頁第146頁第147頁第148頁第149頁第150頁第151頁第152頁第153頁第154頁第155頁第156頁第157頁第158頁第159頁第160頁第161頁第162頁第163頁第164頁第165頁第166頁第167頁第168頁第169頁第170頁第171頁第172頁

S1C63567 TECHNICAL MANUAL

EPSON

29

CHAPTER 4: PERIPHERAL CIRCUITS AND OPERATION (Input Ports)

The interrupt selection register (SIK) and input comparison register (KCP) are individually set for the

input ports K00–K03 and K10–K13, and can specify the terminals for generating interrupt and interrupt

timing.

The interrupt selection registers (SIK00–SIK03, SIK10–SIK13) select what input of K00–K03 and K10–K13

to use for the interrupt. Writing "1" into an interrupt selection register incorporates that input port into

the interrupt generation conditions. The changing the input port where the interrupt selection register

has been set to "0" does not affect the generation of the interrupt.

The input interrupt timing can select that the interrupt be generated at the rising edge of the input or that

it be generated at the falling edge according to the set value of the input comparison registers (KCP00–

KCP03, KCP10–KCP13).

By setting these two conditions, the interrupt for K00–K03 or K10–K13 is generated when input ports in

which an interrupt has been enabled by the input selection registers and the contents of the input com-

parison registers have been changed from matching to no matching.

The interrupt mask registers (EIK0, EIK1) enable the interrupt mask to be selected for K00–K03 and K10–

K13.

When the interrupt is generated, the interrupt factor flag (IK0, IK1) is set to "1".

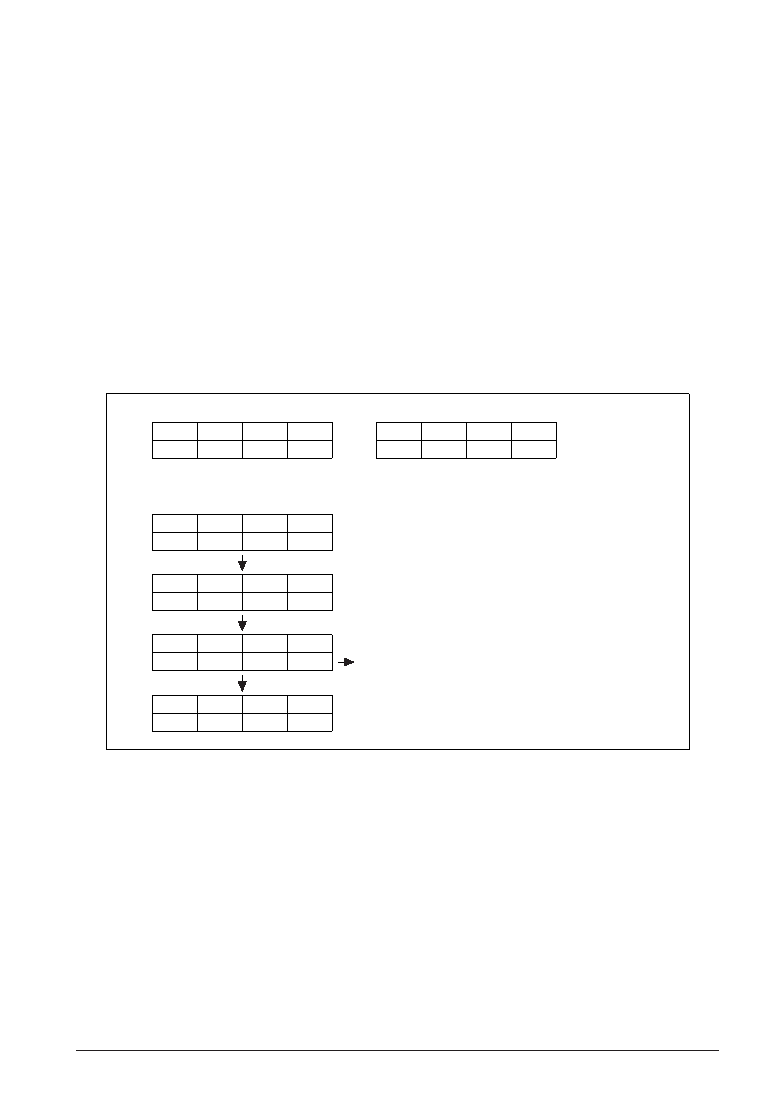

Figure 4.4.2.2 shows an example of an interrupt for K00–K03.

Interrupt selection register

SIK03

1

SIK02

1

SIK01

1

SIK00

0

Input port

(1)

(Initial value)

Interrupt generation

K03

1

K02

0

K01

1

K00

0

Input comparison register

KCP03

1

KCP02

0

KCP01

1

KCP00

0

With the above setting, the interrupt of K00–K03 is generated under the following condition:

(2)

K03

1

K02

0

K01

1

K00

1

(3)

K03

0

K02

0

K01

1

K00

1

(4)

K03

0

K02

1

K01

1

K00

1

Because K00 interrupt is set to disable, interrupt will be

generated when no matching occurs between the

contents of the 3 bits K01–K03 and the 3 bits input

comparison register KCP01–KCP03.

Fig. 4.4.2.2 Example of interrupt of K00–K03

K00 interrupt is disabled by the interrupt selection register (SIK00), so that an interrupt does not occur at

(2). At (3), K03 changes to "0"; the data of the terminals that are interrupt enabled no longer match the

data of the input comparison registers, so that interrupt occurs. As already explained, the condition for

the interrupt to occur is the change in the port data and contents of the input comparison registers from

matching to no matching. Hence, in (4), when the no matching status changes to another no matching

status, an interrupt does not occur. Further, terminals that have been masked for interrupt do not affect

the conditions for interrupt generation.

4.4.3 Mask option

Internal pull-up resistor can be selected for each of the eight bits of the input ports (K00–K03, K10–K13)

with the input port mask option.

When "Gate direct" is selected, take care that the floating status does not occur for the input. Select "With

pull-up resistor" for input ports that are not being used.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| S1C63653F | 4-BIT, FLASH, 4 MHz, MICROCONTROLLER, CQFP100 |

| S1C6F567D0A0100 | MICROCONTROLLER, UUC141 |

| S1C6N3B0D0A0100 | MICROCONTROLLER, UUC54 |

| S1C6P366D0A0100 | 4-BIT, FLASH, 4.1 MHz, MICROCONTROLLER, UUC102 |

| S1C6P466D0A0A00 | MICROCONTROLLER, UUC140 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| S1C63616 | 制造商:EPSON 制造商全稱:EPSON 功能描述:4-bit Single Chip Microcomputer |

| S1C63632 | 制造商:EPSON 制造商全稱:EPSON 功能描述:4-bit Single Chip Microcomputer |

| S1C63653 | 制造商:EPSON 制造商全稱:EPSON 功能描述:CMOS 4-bit Single Chip Microcontroller |

| S1C63656 | 制造商:EPSON 制造商全稱:EPSON 功能描述:4-bit Single Chip Microcomputer |

| S1C63657 | 制造商:EPSON 制造商全稱:EPSON 功能描述:CMOS 4-bit Single Chip Microcontroller |

發(fā)布緊急采購,3分鐘左右您將得到回復。