- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄383724 > ORT8850L Field-Programmable System Chip (FPSC) Eight-Channel x 850 Mbits/s Backplane Transceiver PDF資料下載

參數(shù)資料

| 型號: | ORT8850L |

| 英文描述: | Field-Programmable System Chip (FPSC) Eight-Channel x 850 Mbits/s Backplane Transceiver |

| 中文描述: | 現(xiàn)場可編程系統(tǒng)芯片(促進文化基金)8通道x 850 Mbits /秒背板收發(fā)器 |

| 文件頁數(shù): | 39/112頁 |

| 文件大小: | 2417K |

| 代理商: | ORT8850L |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁當前第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁第107頁第108頁第109頁第110頁第111頁第112頁

Agere Systems Inc.

39

Data Sheet

August 2001

Eight-Channel x 850 Mbits/s Backplane Transceiver

ORCA

ORT8850 FPSC

Memory Map

(continued)

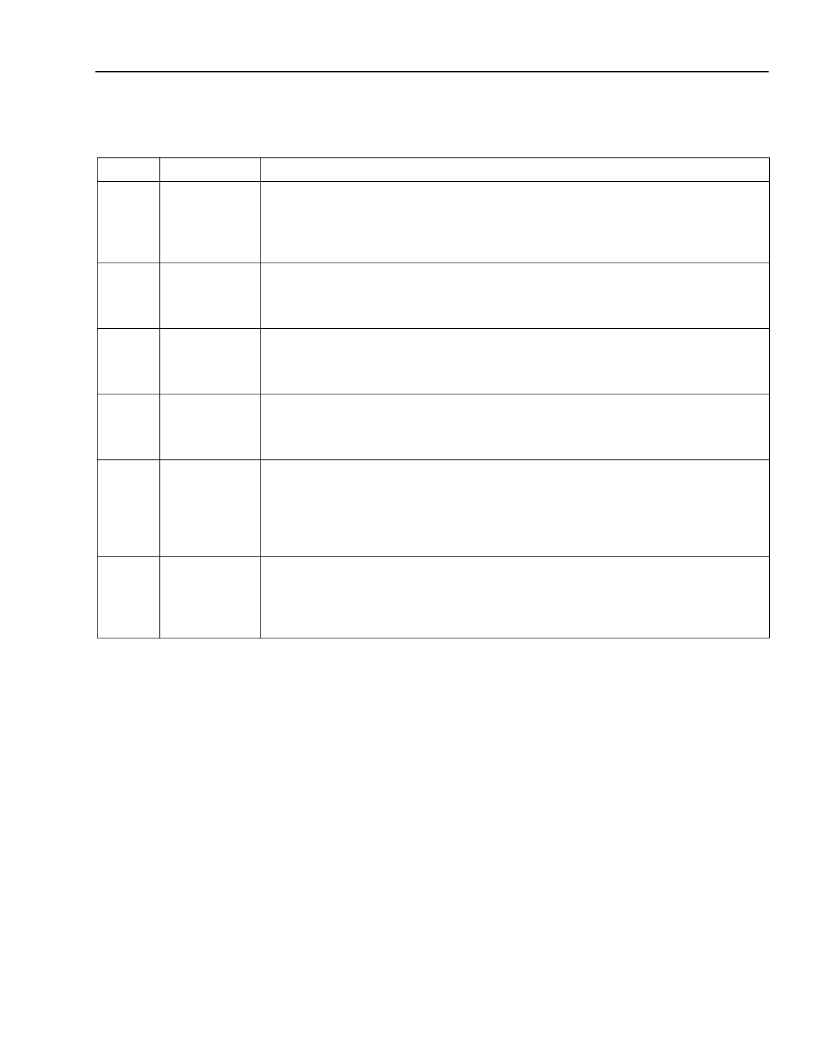

Table 10. Structural Register Elements

Registers Access and General Description

The memory map comprises three address blocks:

I

Generic register block: ID, revision, scratch pad, lock, FIFO alignment, and reset registers.

I

Device register block: control and status bits, common to the four channels in each of the two quad interfaces.

I

Channel register blocks: each of the four channels in both quads have an address block. The four address

blocks in both quads have the same structure, with a constant address offset between channel register blocks.

All registers are write-protected by the lock register, except for the scratch pad register. The lock register is a 16-bit

read/write register. Write access is given to registers only when the key value 0x0580 is present in the lock register.

An error flag will be set upon detecting a write access when write permission is denied. The default value is

0x0000.

After powerup reset or soft reset, unused register bits will be read as zeros. Unused address locations are also

read as zeros. Write-only register bits will be read as zeros. The detailed information on register access and func-

tion are described on the tables, memory map, and memory map bit description.

A memory map is included in Table 11, followed by detailed descriptions in Table 11. These tables list only the

memory map for the core registers of the ORT8850 device. The remaining FPGA registers can be found in the

Series 4 data sheet.

Element

sreg

Register

Status

Register

Description

A status register is read only, and, as the name implies, is used to convey the status

information of a particular element or function of the ORT8850 core. The reset value of

an sreg is really the reset value of the particular element or function that is being read.

In some cases, an sreg is really a fixed value; an example of which is the fixed ID and

revision registers.

A control register is read and writable memory element inside core control. The value of

a creg will always be the value written to it. Events inside the ORT8850 core cannot

affect creg value. The only exception is a soft reset, in which case the creg will return to

its default value.

Each element, or bit, of a pulse register is a control or event signal that is asserted and

then deasserted when a value of one is written to it. This means that each bit is always

of value 0 until it is written to, upon which it is pulsed to the value of one and then

returned to a value of 0. A pulse register will always have a read value of 0.

Each bit of an interrupt alarm register is an event latch. When a particular event is pro-

duced in the ORT8850 core, its occurrence is latched by its associated iareg bit. To

clear a particular iareg bit, a value of one must be written to it. In the ORT8850 core, all

isreg reset values are 0.

Each bit of an interrupt status register is physically the logical-OR function. It is a con-

solidation of lower-level interrupt alarms and/or isreg bits from other registers. A direct

result of the fact that each bit of the isreg is a logical-OR function means that it will have

a read value of one if any of the consolidation signals are of value one, and will be of

value 0 if and only if all consolidation signals are of value 0. In the ORT8850 core, all

isreg default values are 0.

Each bit of a status register or alarm register has an associated enable bit. If this bit is

set to value one, then the event is allowed to propagate to the next higher level of con-

solidation. If this bit is set to zero, then the associated iareg or isreg bit can still be

asserted but an alarm will not propagate to the next higher level. An interrupt enable bit

is an interrupt mask bit when it is set to value 0.

creg

Control

Register

preg

Pulse

Register

iareg

Interrupt Alarm

Register

isreg

Interrupt Status

Register

ereg

Interrupt Enable

Register

相關PDF資料 |

PDF描述 |

|---|---|

| OS1001 | Interface IC |

| OS1010 | Optoelectronic |

| OS1011 | SINGLE 1.8V, 200 KHZ OP, E TEMP, -40C to +125C, 8-PDIP, TUBE |

| OS1012 | 1.8V, 200kHz single low-cost, CMOS Op Amplifier on 120K Analog ROM process., -40C to +125C, 8-MSOP, T/R |

| OS1013 | 1.8V, 200kHz single low-cost, CMOS Op Amplifier on 120K Analog ROM proccess., -40C to +125C, 5-SOT-23, T/R |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| ORT8850L-1BM680C | 功能描述:FPGA - 現(xiàn)場可編程門陣列 4992 LUT 278 I/O RoHS:否 制造商:Altera Corporation 系列:Cyclone V E 柵極數(shù)量: 邏輯塊數(shù)量:943 內(nèi)嵌式塊RAM - EBR:1956 kbit 輸入/輸出端數(shù)量:128 最大工作頻率:800 MHz 工作電源電壓:1.1 V 最大工作溫度:+ 70 C 安裝風格:SMD/SMT 封裝 / 箱體:FBGA-256 |

| ORT8850L-1BM680I | 功能描述:FPGA - 現(xiàn)場可編程門陣列 4992 LUT 278 I/O RoHS:否 制造商:Altera Corporation 系列:Cyclone V E 柵極數(shù)量: 邏輯塊數(shù)量:943 內(nèi)嵌式塊RAM - EBR:1956 kbit 輸入/輸出端數(shù)量:128 最大工作頻率:800 MHz 工作電源電壓:1.1 V 最大工作溫度:+ 70 C 安裝風格:SMD/SMT 封裝 / 箱體:FBGA-256 |

| ORT8850L-1BMN680C | 功能描述:FPGA - 現(xiàn)場可編程門陣列 4992 LUT 278 I/O RoHS:否 制造商:Altera Corporation 系列:Cyclone V E 柵極數(shù)量: 邏輯塊數(shù)量:943 內(nèi)嵌式塊RAM - EBR:1956 kbit 輸入/輸出端數(shù)量:128 最大工作頻率:800 MHz 工作電源電壓:1.1 V 最大工作溫度:+ 70 C 安裝風格:SMD/SMT 封裝 / 箱體:FBGA-256 |

| ORT8850L-1BMN680I | 功能描述:FPGA - 現(xiàn)場可編程門陣列 4992 LUT 278 I/O RoHS:否 制造商:Altera Corporation 系列:Cyclone V E 柵極數(shù)量: 邏輯塊數(shù)量:943 內(nèi)嵌式塊RAM - EBR:1956 kbit 輸入/輸出端數(shù)量:128 最大工作頻率:800 MHz 工作電源電壓:1.1 V 最大工作溫度:+ 70 C 安裝風格:SMD/SMT 封裝 / 箱體:FBGA-256 |

| ORT8850L-2BM680C | 功能描述:FPGA - 現(xiàn)場可編程門陣列 4992 LUT 278 I/O RoHS:否 制造商:Altera Corporation 系列:Cyclone V E 柵極數(shù)量: 邏輯塊數(shù)量:943 內(nèi)嵌式塊RAM - EBR:1956 kbit 輸入/輸出端數(shù)量:128 最大工作頻率:800 MHz 工作電源電壓:1.1 V 最大工作溫度:+ 70 C 安裝風格:SMD/SMT 封裝 / 箱體:FBGA-256 |

發(fā)布緊急采購,3分鐘左右您將得到回復。