- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄180243 > M7A3PE600-FFGG256I FPGA, 600000 GATES, PBGA256 PDF資料下載

參數(shù)資料

| 型號(hào): | M7A3PE600-FFGG256I |

| 元件分類(lèi): | FPGA |

| 英文描述: | FPGA, 600000 GATES, PBGA256 |

| 封裝: | 1 MM PITCH, GREEN, FBGA-256 |

| 文件頁(yè)數(shù): | 142/168頁(yè) |

| 文件大?。?/td> | 1335K |

| 代理商: | M7A3PE600-FFGG256I |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)第69頁(yè)第70頁(yè)第71頁(yè)第72頁(yè)第73頁(yè)第74頁(yè)第75頁(yè)第76頁(yè)第77頁(yè)第78頁(yè)第79頁(yè)第80頁(yè)第81頁(yè)第82頁(yè)第83頁(yè)第84頁(yè)第85頁(yè)第86頁(yè)第87頁(yè)第88頁(yè)第89頁(yè)第90頁(yè)第91頁(yè)第92頁(yè)第93頁(yè)第94頁(yè)第95頁(yè)第96頁(yè)第97頁(yè)第98頁(yè)第99頁(yè)第100頁(yè)第101頁(yè)第102頁(yè)第103頁(yè)第104頁(yè)第105頁(yè)第106頁(yè)第107頁(yè)第108頁(yè)第109頁(yè)第110頁(yè)第111頁(yè)第112頁(yè)第113頁(yè)第114頁(yè)第115頁(yè)第116頁(yè)第117頁(yè)第118頁(yè)第119頁(yè)第120頁(yè)第121頁(yè)第122頁(yè)第123頁(yè)第124頁(yè)第125頁(yè)第126頁(yè)第127頁(yè)第128頁(yè)第129頁(yè)第130頁(yè)第131頁(yè)第132頁(yè)第133頁(yè)第134頁(yè)第135頁(yè)第136頁(yè)第137頁(yè)第138頁(yè)第139頁(yè)第140頁(yè)第141頁(yè)當(dāng)前第142頁(yè)第143頁(yè)第144頁(yè)第145頁(yè)第146頁(yè)第147頁(yè)第148頁(yè)第149頁(yè)第150頁(yè)第151頁(yè)第152頁(yè)第153頁(yè)第154頁(yè)第155頁(yè)第156頁(yè)第157頁(yè)第158頁(yè)第159頁(yè)第160頁(yè)第161頁(yè)第162頁(yè)第163頁(yè)第164頁(yè)第165頁(yè)第166頁(yè)第167頁(yè)第168頁(yè)

ProASIC3E Flash Family FPGAs

A d v an c ed v0 . 5

3-7

Power Consumption of Various Internal Resources

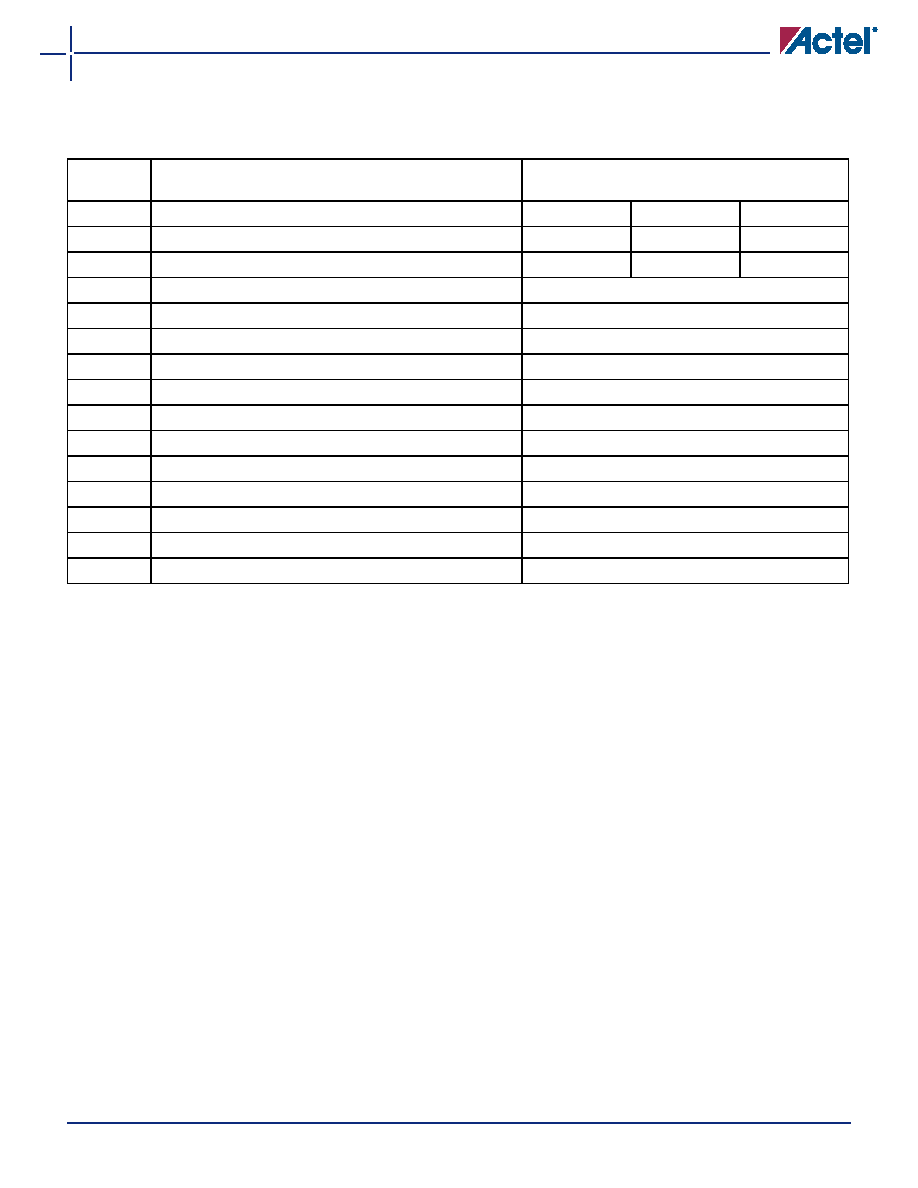

Table 3-10 Different Components Contributing to the Dynamic Power Consumption in ProASIC3E Devices

Parameter

Definition

Device-Specific Dynamic Contributions

(

W/MHz)

A3PE600

A3PE1500

A3PE3000

PAC1

Clock contribution of a Global Rib

12.77

16.21

19.7

PAC2

Clock contribution of a Global Spine

1.85

3.06

4.16

PAC3

Clock contribution of a VersaTile row

0.88

PAC4

Clock contribution of a VersaTile used as a sequential module

0.12

PAC5

First contribution of a VersaTile used as a sequential module

0.07

PAC6

Second contribution of a VersaTile used as a sequential module

0.29

PAC7

Contribution of a VersaTile used as a combinatorial module

0.29

PAC8

Average contribution of a routing net

0.70

P

Contribution of an I/O input pin (standard dependent)

PAC10

Contribution of an I/O output pin (standard dependent)

PAC11

Average contribution of a RAM block during a read operation

25.00

PAC12

Average contribution of a RAM block during a write operation

30.00

PAC13

First contribution of a PLL

4.00

PAC14

Second contribution of a PLL

2.00

Note: *For a different output load, drive strength, or slew rate, Actel recommends using the Actel

power calculator or SmartPower in Actel Libero IDE software.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| M7A3PE600-FFGG484I | FPGA, 600000 GATES, PBGA484 |

| M7A3PE600-FPQ208I | FPGA, 600000 GATES, PQFP208 |

| M7A3PE600-FPQG208I | FPGA, 600000 GATES, PQFP208 |

| M7R-R63FAJFREQ | CRYSTAL OSCILLATOR, CLOCK, 80.001 MHz - 125 MHz, CMOS/TTL OUTPUT |

| M7R-R68TAJFREQ | CRYSTAL OSCILLATOR, CLOCK, 80.001 MHz - 125 MHz, CMOS/TTL OUTPUT |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| M7A5 | 制造商:未知廠家 制造商全稱(chēng):未知廠家 功能描述:MEDIUM CURRENT SILICON RECTIFIERS |

| M7A9 | 制造商:未知廠家 制造商全稱(chēng):未知廠家 功能描述:MEDIUM CURRENT SILICON RECTIFIERS |

| M7AFS600-1FG256 | 制造商:Microsemi Corporation 功能描述:FPGA FUSION 600K GATES 1282.05MHZ 130NM 1.5V 256FBGA - Trays 制造商:Microsemi SOC Products Group 功能描述:FPGA FUSION 600K GATES 1282.05MHZ 130NM 1.5V 256FBGA - Trays |

| M7AFS600-1FG256ES | 制造商:ACTEL 制造商全稱(chēng):Actel Corporation 功能描述:Actel Fusion Mixed-Signal FPGAs |

| M7AFS600-1FG256I | 制造商:Microsemi Corporation 功能描述:FPGA FUSION 600K GATES 1282.05MHZ 130NM 1.5V 256FBGA - Trays 制造商:Microsemi SOC Products Group 功能描述:FPGA FUSION 600K GATES 1282.05MHZ 130NM 1.5V 256FBGA - Trays |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。