- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄180243 > M7A3PE600-FFGG256I FPGA, 600000 GATES, PBGA256 PDF資料下載

參數(shù)資料

| 型號: | M7A3PE600-FFGG256I |

| 元件分類: | FPGA |

| 英文描述: | FPGA, 600000 GATES, PBGA256 |

| 封裝: | 1 MM PITCH, GREEN, FBGA-256 |

| 文件頁數(shù): | 107/168頁 |

| 文件大小: | 1335K |

| 代理商: | M7A3PE600-FFGG256I |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁當前第107頁第108頁第109頁第110頁第111頁第112頁第113頁第114頁第115頁第116頁第117頁第118頁第119頁第120頁第121頁第122頁第123頁第124頁第125頁第126頁第127頁第128頁第129頁第130頁第131頁第132頁第133頁第134頁第135頁第136頁第137頁第138頁第139頁第140頁第141頁第142頁第143頁第144頁第145頁第146頁第147頁第148頁第149頁第150頁第151頁第152頁第153頁第154頁第155頁第156頁第157頁第158頁第159頁第160頁第161頁第162頁第163頁第164頁第165頁第166頁第167頁第168頁

ProASIC3E Flash Family FPGAs

A d v an c ed v0 . 5

2-31

Features Supported on Every I/O

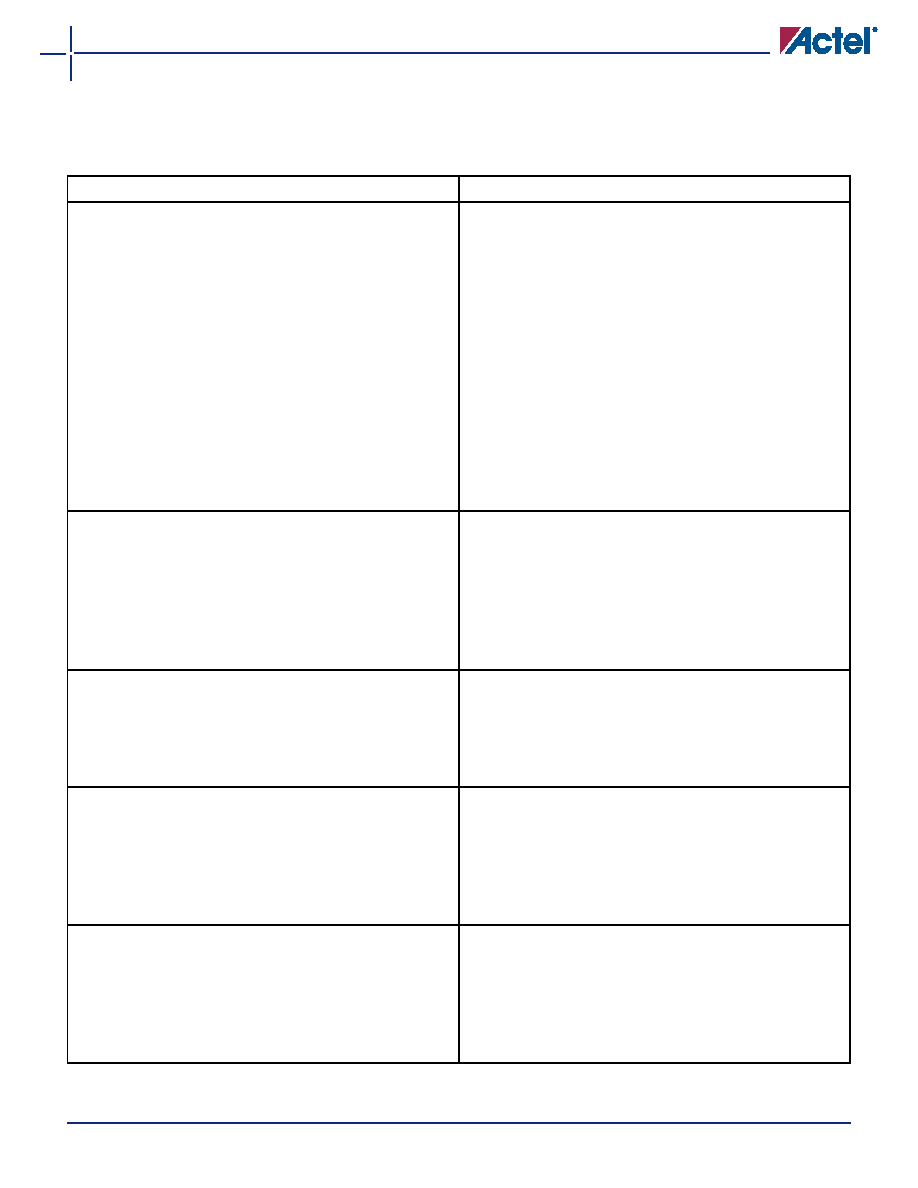

Table 2-15 lists all features supported by transmitter/receiver for single-ended and differential I/Os.

Table 2-15 I/O Features ProASIC3E

Feature

Description

Single-Ended and Voltage-Referenced Transmitter Features

Hot insertion in every mode except PCI or 5 V input tolerant

(these modes use clamp diodes and do not allow hot insertion)

Activation of hot insertion (disabling the clamp diode) is

selectable by I/Os

Weak pull-up and pull-down

Two slew rates

Skew between output buffer enable/disable time: 2 ns delay

on the rising edge and 0 ns delay on the falling edge (see the

Time" section on page 2-43 for more information).

Five drive strengths

5 V tolerant receiver ("5 V Input Tolerance" section on page 2-

38)

LVTTL/LVCMOS 3.3 V outputs compatible with 5 V TTL inputs

High Performance (Table 2-16 on page 2-32

)

Single-Ended Receiver Features

ESD protection

Schmitt Trigger option

Programmable Delay: 0 ns if bypassed, 0.46 ns with 000

setting, 4.66 ns with 111 setting, 0.6 ns intermediate delay

increments (at 25°C, 1.5 V)

High performance (Table 2-16 on page 2-32)

Separate ground plane for GNDQ pin and power plane for VMV

pin are used for input buffer to reduce output induced noise.

Voltage-Referenced Differential Receiver Features

Programmable Delay: 0 ns if bypassed, 0.46 ns with 000

setting, 4.66 ns with 111 setting, 0.6 ns intermediate delay

increments (at 25°C, 1.5 V)

High performance (Table 2-16 on page 2-32)

Separate ground plane for GNDQ pin and power plane for VMV

pin are used for input buffer to reduce output induced noise.

CMOS-Style LVDS, BLVDS, M-LVDS or LVPECL Transmitter

Two I/Os and external resistors are used to provide a CMOS-

style LVDS, DDR LVDS, BLVDS, and M-LVDS or LVPECL

transmitter solution.

Activation of hot insertion (disabling the clamp diode) is

selectable by I/Os.

Weak pull-up and pull-down

High slew rate

LVDS, DDR LVDS, BLVDS, and M-LVDS/LVPECL Differential Receiver

Features

ESD protection

High performance (Table 2-16 on page 2-32)

Programmable Delay: 0 ns if bypassed, 0.46 ns with 000

setting, 4.66 ns with 111 setting, 0.6 ns intermediate delay

increments (at 25°C, 1.5 V)

Separate input buffer ground and power planes to avoid

output-induced noise in the input circuitry

相關PDF資料 |

PDF描述 |

|---|---|

| M7A3PE600-FFGG484I | FPGA, 600000 GATES, PBGA484 |

| M7A3PE600-FPQ208I | FPGA, 600000 GATES, PQFP208 |

| M7A3PE600-FPQG208I | FPGA, 600000 GATES, PQFP208 |

| M7R-R63FAJFREQ | CRYSTAL OSCILLATOR, CLOCK, 80.001 MHz - 125 MHz, CMOS/TTL OUTPUT |

| M7R-R68TAJFREQ | CRYSTAL OSCILLATOR, CLOCK, 80.001 MHz - 125 MHz, CMOS/TTL OUTPUT |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| M7A5 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:MEDIUM CURRENT SILICON RECTIFIERS |

| M7A9 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:MEDIUM CURRENT SILICON RECTIFIERS |

| M7AFS600-1FG256 | 制造商:Microsemi Corporation 功能描述:FPGA FUSION 600K GATES 1282.05MHZ 130NM 1.5V 256FBGA - Trays 制造商:Microsemi SOC Products Group 功能描述:FPGA FUSION 600K GATES 1282.05MHZ 130NM 1.5V 256FBGA - Trays |

| M7AFS600-1FG256ES | 制造商:ACTEL 制造商全稱:Actel Corporation 功能描述:Actel Fusion Mixed-Signal FPGAs |

| M7AFS600-1FG256I | 制造商:Microsemi Corporation 功能描述:FPGA FUSION 600K GATES 1282.05MHZ 130NM 1.5V 256FBGA - Trays 制造商:Microsemi SOC Products Group 功能描述:FPGA FUSION 600K GATES 1282.05MHZ 130NM 1.5V 256FBGA - Trays |

發(fā)布緊急采購,3分鐘左右您將得到回復。