- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄360998 > ISP1161BD (NXP SEMICONDUCTORS) Full-speed Universal Serial Bus single-chip host and device controller PDF資料下載

參數(shù)資料

| 型號: | ISP1161BD |

| 廠商: | NXP SEMICONDUCTORS |

| 元件分類: | 總線控制器 |

| 英文描述: | Full-speed Universal Serial Bus single-chip host and device controller |

| 中文描述: | UNIVERSAL SERIAL BUS CONTROLLER, PQFP64 |

| 封裝: | 10 X 10 MM, 1.40 MM HEIGHT, PLASTIC, MS-026, SOT-314-2, LQFP-64 |

| 文件頁數(shù): | 48/127頁 |

| 文件大小: | 2762K |

| 代理商: | ISP1161BD |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁當(dāng)前第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁第107頁第108頁第109頁第110頁第111頁第112頁第113頁第114頁第115頁第116頁第117頁第118頁第119頁第120頁第121頁第122頁第123頁第124頁第125頁第126頁第127頁

Philips Semiconductors

ISP1161

Full-speed USB single-chip host and device controller

Product data

Rev. 01 — 3 July 2001

48 of 130

9397 750 08313

Philips Electronics N.V. 2001. All rights reserved.

12. DMA transfer for the Device Controller

Direct Memory Access (DMA) is a method to transfer data from one location to

another in a computer system, without intervention of the Central Processor Unit

(CPU). Many different implementations of DMA exist. The ISP1161 DC supports two

methods:

8237 compatible mode

: based on the DMA subsystem of the IBM personal

computers (PC, AT and all its successors and clones); this architecture uses the

Intel 8237 DMA controller and has separate address spaces for memory and I/O

DACK-only mode

: based on the DMA implementation in some embedded RISC

processors, which has a single address space for both memory and I/O.

The ISP1161 DC supports DMA transfer for all 14 configurable endpoints (see

Table 7

). Only one endpoint at a time can be selected for DMA transfer. The DMA

operation of the ISP1161 DC can be interleaved with normal I/O mode access to

other endpoints.

The following features are supported:

Single-cycle or burst transfers (up to 16 bytes per cycle)

Programmable transfer direction (read or write)

Multiple End-Of-Transfer (EOT) sources: external pin, internal conditions,

short/empty packet

Programmable signal levels on pins DREQ2, DACK2 and EOT.

12.1 Selecting an endpoint for DMA transfer

The target endpoint for DMA access is selected via bits EPDIX[3:0] in the DMA

Configuration Register, as shown in

Table 10

. The transfer direction (read or write) is

automatically set by bit EPDIR in the associated ECR, to match the selected endpoint

type (OUT endpoint: read; IN endpoint: write).

Asserting input DACK2 automatically selects the endpoint specified in the DMA

Configuration Register, regardless of the current endpoint used for I/O mode access.

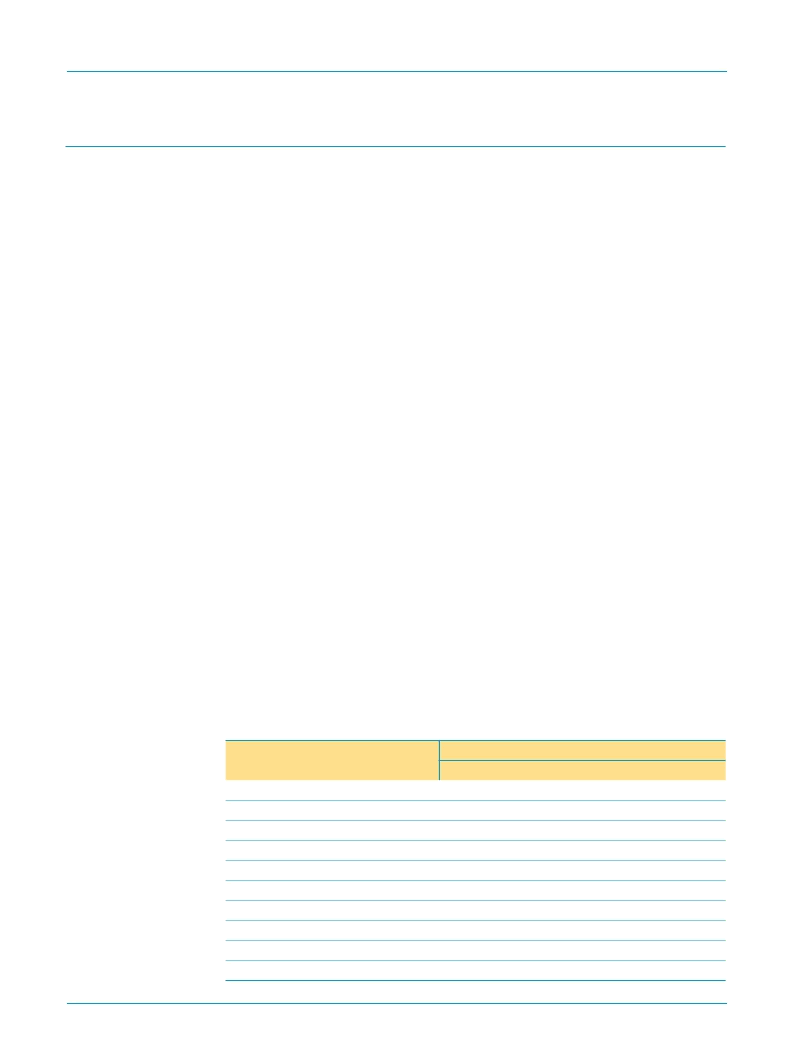

Table 10: Endpoint selection for DMA transfer

Endpoint

identifier

EPIDX[3:0]

Transfer direction

EPDIR = 0

OUT: read

OUT: read

OUT: read

OUT: read

OUT: read

OUT: read

OUT: read

OUT: read

OUT: read

OUT: read

EPDIR = 1

IN: write

IN: write

IN: write

IN: write

IN: write

IN: write

IN: write

IN: write

IN: write

IN: write

1

2

3

4

5

6

7

8

9

0010

0011

0100

0101

0110

0111

1000

1001

1010

1011

10

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| ISP1161BM | Full-speed Universal Serial Bus single-chip host and device controller |

| ISP1181ABS | INDUCTOR 1.0NH +-.3NH FIXED SMD |

| ISP1181A | Full-speed Universal Serial Bus peripheral controller |

| ISP1181ADGG | Full-speed Universal Serial Bus peripheral controller |

| ISP1181B | Full-speed Universal Serial Bus peripheral controller |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| ISP1161BM | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:Full-speed Universal Serial Bus single-chip host and device controller |

| ISP1181 | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:Full-speed Universal Serial Bus interface device |

| ISP1181A | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:Full-speed Universal Serial Bus peripheral controller |

| ISP1181ABS | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:Full-speed Universal Serial Bus peripheral controller |

| ISP1181ABS,518 | 功能描述:USB 接口集成電路 USB 1.1 ADV DEVICE RoHS:否 制造商:Cypress Semiconductor 產(chǎn)品:USB 2.0 數(shù)據(jù)速率: 接口類型:SPI 工作電源電壓:3.15 V to 3.45 V 工作電源電流: 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:WLCSP-20 |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。