- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄224000 > HYS64T16000HDL-2.5-A (INFINEON TECHNOLOGIES AG) 16M X 64 DDR DRAM MODULE, 0.4 ns, DMA200 PDF資料下載

參數(shù)資料

| 型號(hào): | HYS64T16000HDL-2.5-A |

| 廠商: | INFINEON TECHNOLOGIES AG |

| 元件分類(lèi): | DRAM |

| 英文描述: | 16M X 64 DDR DRAM MODULE, 0.4 ns, DMA200 |

| 封裝: | GREEN, SODIMM-200 |

| 文件頁(yè)數(shù): | 46/46頁(yè) |

| 文件大小: | 833K |

| 代理商: | HYS64T16000HDL-2.5-A |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)當(dāng)前第46頁(yè)

Data Sheet

6

Rev. 1.1, 2005-06

02182004-HWZ1-64OM

HYS64T[16/32/64]0xxxHDL–[2.5/3.7/5]–A

Small Outline DDR2 SDRAM Modules

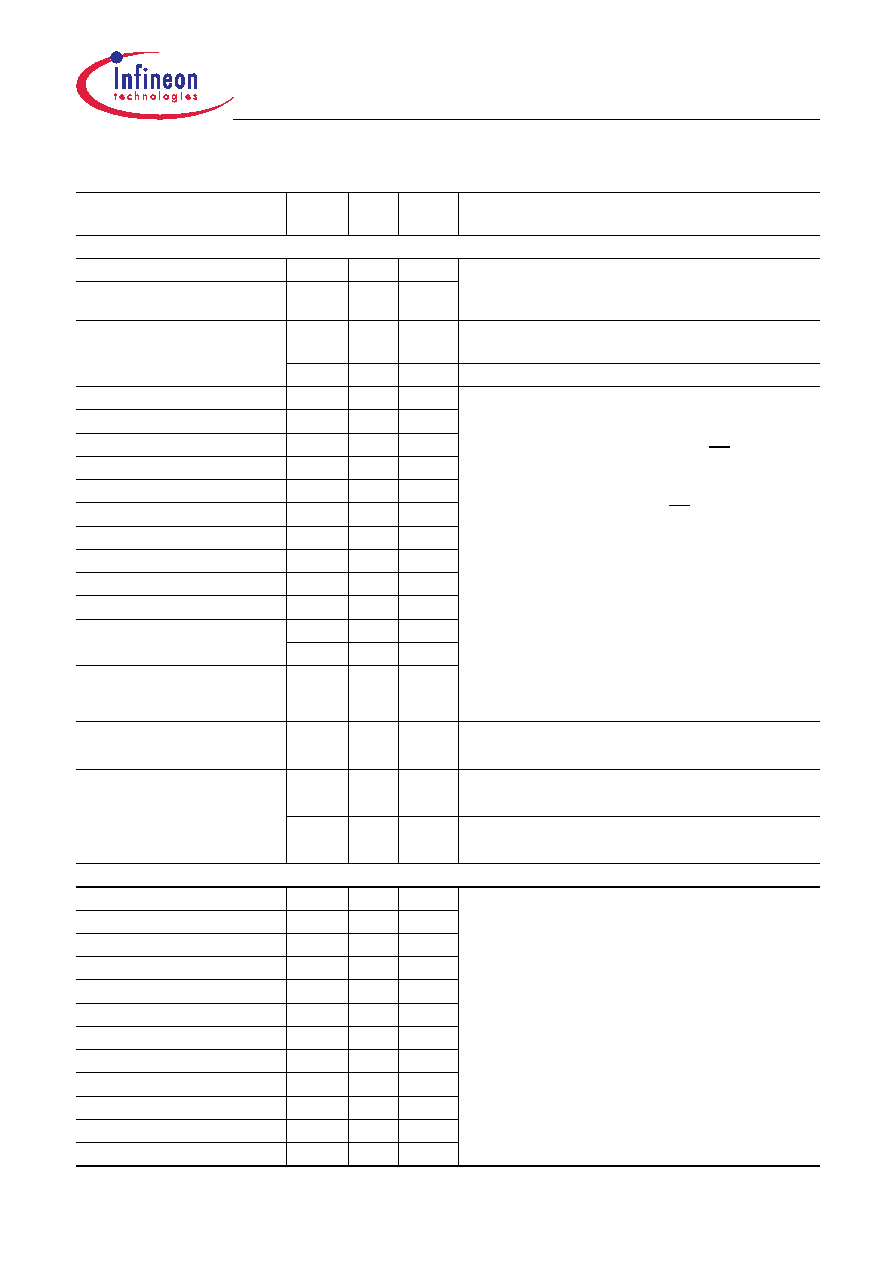

Pin Configuration and Block Diagrams

Address Signals

107

BA0

I

SSTL

Bank Address Bus 2:0

Selects which DDR2 SDRAM internal bank of four or

eight is activated.

106

BA1

I

SSTL

85

BA2

I

SSTL

Bank Address Bus 2

Greater than 512Mb DDR2 SDRAMS

NC

SSTL

Less than 1Gb DDR2 SDRAMS

102

A0

I

SSTL

Address Bus 12:0

During a Bank Activate command cycle, defines the

row address when sampled at the crosspoint of the

rising edge of CK and falling edge of CK. During a

Read or Write command cycle, defines the column

address when sampled at the cross point of the rising

edge of CK and falling edge of CK. In addition to the

column address, AP is used to invoke autoprecharge

operation at the end of the burst read or write cycle. If

AP is HIGH, autoprecharge is selected and BA0-BAn

defines the bank to be precharged. If AP is LOW,

autoprecharge is disabled. During a Precharge

command cycle, AP is used in conjunction with BA0-

BAn to control which bank(s) to precharge. If AP is

HIGH, all banks will be precharged regardless of the

state of BA0-BAn inputs. If AP is LOW, then BA0-BAn

are used to define which bank to precharge.

101

A1

I

SSTL

100

A2

I

SSTL

99

A3

I

SSTL

98

A4

I

SSTL

97

A5

I

SSTL

94

A6

I

SSTL

92

A7

I

SSTL

93

A8

I

SSTL

91

A9

I

SSTL

105

A10

I

SSTL

AP

I

SSTL

90

A11

I

SSTL

89

A12

I

SSTL

Address Signal 12

Note: Module based on 256 Mbit or larger dies

116

A13

I

SSTL

Address Signal 13

Note: 1 Gbit based module

NC

—

Not Connected

Note: Module based on 512 Mbit or smaller dies

Data Signals

5

DQ0

I/O

SSTL

Data Bus 63:0

Note: Data Input/Output pins

7

DQ1

I/O

SSTL

17

DQ2

I/O

SSTL

19

DQ3

I/O

SSTL

4

DQ4

I/O

SSTL

6

DQ5

I/O

SSTL

14

DQ6

I/O

SSTL

16

DQ7

I/O

SSTL

23

DQ8

I/O

SSTL

25

DQ9

I/O

SSTL

35

DQ10

I/O

SSTL

37

DQ11

I/O

SSTL

Table 6

Pin Configuration of SO-DIMM (cont’d)

Pin or Ball No.

Name

Pin

Type

Buffer

Type

Function

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| HYS72D64020GR-7-X | 64M X 72 DDR DRAM MODULE, 0.75 ns, DMA184 |

| HYS72D64020GR-7.5-X | 64M X 72 DDR DRAM MODULE, 0.75 ns, DMA184 |

| HYS72T128000EU-2.5-C2 | 128M X 72 DDR DRAM MODULE, 0.4 ns, DMA240 |

| HYS72T64000EP-3.7-B2 | 64M X 72 DDR DRAM MODULE, DMA240 |

| HZ20-1 | 19.25 V, 0.5 W, SILICON, UNIDIRECTIONAL VOLTAGE REGULATOR DIODE, DO-35 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| HYS64T16000HU | 制造商:QIMONDA 制造商全稱(chēng):QIMONDA 功能描述:240-Pin Unbuffered DDR2 SDRAM Modules |

| HYS64T16000HU-3.7-A | 制造商:QIMONDA 制造商全稱(chēng):QIMONDA 功能描述:240-Pin Unbuffered DDR2 SDRAM Modules |

| HYS64T16000HU-5-A | 制造商:QIMONDA 制造商全稱(chēng):QIMONDA 功能描述:240-Pin Unbuffered DDR2 SDRAM Modules |

| HYS64T256020EDL | 制造商:QIMONDA 制造商全稱(chēng):QIMONDA 功能描述:200-Pin SO-DIMM DDR2 SDRAM Modules |

| HYS64T256020EDL-2.5-C | 制造商:QIMONDA 制造商全稱(chēng):QIMONDA 功能描述:200-Pin SO-DIMM DDR2 SDRAM Modules |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。