- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄370620 > HM5212805F (Hitachi,Ltd.) 128M LVTTL interface SDRAM(128M LVTTL 接口同步DRAM) PDF資料下載

參數(shù)資料

| 型號(hào): | HM5212805F |

| 廠商: | Hitachi,Ltd. |

| 英文描述: | 128M LVTTL interface SDRAM(128M LVTTL 接口同步DRAM) |

| 中文描述: | 128M的LVTTL接口的SDRAM(128M的LVTTL接口同步的DRAM) |

| 文件頁數(shù): | 14/63頁 |

| 文件大小: | 858K |

| 代理商: | HM5212805F |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁當(dāng)前第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁

HM5212165F/HM5212805F-75/A60/B60

14

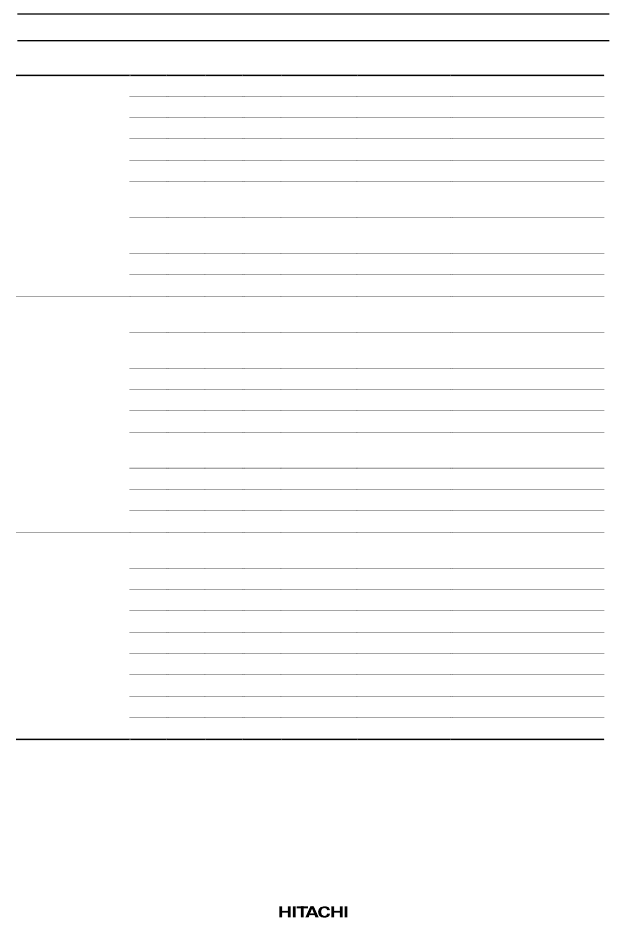

Current state

CS

RAS

CAS

WE

Address

Command

Operation

Write

H

×

×

×

×

×

×

DESL

Continue burst to end

L

H

H

H

NOP

Continue burst to end

L

H

H

L

BST

Burst stop on full page

L

H

L

H

BA, CA, A10 READ/READ A

Term burst and New read

L

H

L

L

BA, CA, A10 WRIT/WRIT A

Term burst and New write

L

L

H

H

BA, RA

ACTV

Other bank active

ILLEGAL on same bank*

3

L

L

H

L

BA, A10

PRE, PALL

Term burst write and

Precharge*

2

L

L

L

H

×

REF, SELF

ILLEGAL

L

L

L

L

MODE

MRS

ILLEGAL

Write with auto-

precharge

H

×

×

×

×

DESL

Continue burst to end and

precharge

L

H

H

H

×

NOP

Continue burst to end and

precharge

L

H

H

L

×

BST

ILLEGAL

L

H

L

H

BA, CA, A10 READ/READ A

ILLEGAL*

4

L

H

L

L

BA, CA, A10 WRIT/WRIT A

ILLEGAL*

4

L

L

H

H

BA, RA

ACTV

Other bank active

ILLEGAL on same bank*

3

L

L

H

L

BA, A10

PRE, PALL

ILLEGAL*

4

L

L

L

H

×

REF, SELF

ILLEGAL

L

L

L

L

MODE

MRS

ILLEGAL

Refresh

(auto-refresh)

H

×

×

×

×

DESL

Enter IDLE after t

RC

L

H

H

H

×

×

NOP

Enter IDLE after t

RC

Enter IDLE after t

RC

ILLEGAL*

5

L

H

H

L

BST

L

H

L

H

BA, CA, A10 READ/READ A

L

H

L

L

BA, CA, A10 WRIT/WRIT A

ILLEGAL*

5

L

L

H

H

BA, RA

ACTV

ILLEGAL*

5

L

L

H

L

BA, A10

PRE, PALL

ILLEGAL*

5

L

L

L

H

×

REF, SELF

ILLEGAL

L

L

L

L

MODE

MRS

ILLEGAL

Notes: 1. H: V

IH

. L: V

IL

.

×

: V

IH

or V

IL

.

The other combinations are inhibit.

2. An interval of t

DPL

is required between the final valid data input and the precharge command.

3. If t

RRD

is not satisfied, this operation is illegal.

4. Illegal for same bank, except for another bank.

5. Illegal for all banks.

6. NOP for same bank, except for another bank.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| HM5212165F | 128M LVTTL interface SDRAM(128M LVTTL 接口同步DRAM) |

| HM5225165BTT-75 | 256M LVTTL interface SDRAM 133 MHz/100 MHz 4-Mword 】 16-bit 】 4-bank/8-Mword 】 8-bit 】 4-bank /16-Mword 】 4-bit 】 4-bank PC/133, PC/100 SDRAM |

| HM5225805BLTT-A6 | 256M LVTTL interface SDRAM 133 MHz/100 MHz 4-Mword 】 16-bit 】 4-bank/8-Mword 】 8-bit 】 4-bank /16-Mword 】 4-bit 】 4-bank PC/133, PC/100 SDRAM |

| HM5225405B-B6 | 256M LVTTL interface SDRAM 133 MHz/100 MHz 4-Mword 】 16-bit 】 4-bank/8-Mword 】 8-bit 】 4-bank /16-Mword 】 4-bit 】 4-bank PC/133, PC/100 SDRAM |

| HM5225405BLTT-75 | POT 20K OHM 9MM HORZ NO BUSHING |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| HM5212805FLTD-75 | 制造商:ELPIDA 制造商全稱:Elpida Memory 功能描述:128M LVTTL interface SDRAM 133 MHz/100 MHz 2-Mword × 16-bit × 4-bank/4-Mword × 8-bit × 4-bank PC/133, PC/100 SDRAM |

| HM5212805FLTD-A60 | 制造商:HITACHI 制造商全稱:Hitachi Semiconductor 功能描述:128M LVTTL interface SDRAM 133 MHz/100 MHz 2-Mword X 16-bit X 4-bank/4-Mword X 8-bit X 4-bank PC/133, PC/100 SDRAM |

| HM5212805FLTD-B60 | 制造商:HITACHI 制造商全稱:Hitachi Semiconductor 功能描述:128M LVTTL interface SDRAM 133 MHz/100 MHz 2-Mword X 16-bit X 4-bank/4-Mword X 8-bit X 4-bank PC/133, PC/100 SDRAM |

| HM5212805FTD-75 | 制造商:ELPIDA 制造商全稱:Elpida Memory 功能描述:128M LVTTL interface SDRAM 133 MHz/100 MHz 2-Mword × 16-bit × 4-bank/4-Mword × 8-bit × 4-bank PC/133, PC/100 SDRAM |

| HM5212805FTD-A60 | 制造商:HITACHI 制造商全稱:Hitachi Semiconductor 功能描述:128M LVTTL interface SDRAM 133 MHz/100 MHz 2-Mword X 16-bit X 4-bank/4-Mword X 8-bit X 4-bank PC/133, PC/100 SDRAM |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。