- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄97874 > EC000UM EC000 Core User's Manual (SCM68000) PDF資料下載

參數(shù)資料

| 型號: | EC000UM |

| 英文描述: | EC000 Core User's Manual (SCM68000) |

| 中文描述: | EC000核心用戶手冊(SCM68000) |

| 文件頁數(shù): | 74/145頁 |

| 文件大小: | 829K |

| 代理商: | EC000UM |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁當(dāng)前第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁第107頁第108頁第109頁第110頁第111頁第112頁第113頁第114頁第115頁第116頁第117頁第118頁第119頁第120頁第121頁第122頁第123頁第124頁第125頁第126頁第127頁第128頁第129頁第130頁第131頁第132頁第133頁第134頁第135頁第136頁第137頁第138頁第139頁第140頁第141頁第142頁第143頁第144頁第145頁

Signal Description

MOTOROLA

EC000 CORE PROCESSOR USER’S MANUAL

2-5

2.4.6 Read-Modify-Write (RMCB)

This active-low, three-state output line is logic low during read-modify-write cycles and indi-

cates an indivisible bus sequence. This is described in 3.1.3 Read-Modify-Write Cycle.

2.5 BUS ARBITRATION CONTROL

The bus request, bus grant, and bus grant acknowledge signals form the bus arbitration con-

trol signals that determine which device will be the bus master device. There are two possi-

ble arbitration protocols: 2-wire and 3-wire. In the 2-wire protocol, BGACKB is not used and

must be negated.

2.5.1 Bus Request (BRB)

This active-low input is the combination of bus request signals from all other devices that

could be bus masters. This signal indicates to the SCM68000 that some other device needs

to become the bus master. Bus requests can be issued at any time during a cycle or

between cycles.

2.5.2 Bus Grant (BGB)

This active-low output indicates to all other potential bus master devices that the SCM68000

will relinquish bus control at the end of the current bus cycle.

2.5.3 Bus Grant Acknowledge (BGACKB)—3-Wire Protocol Only

This active-low input indicates that some other device has become the bus master. This sig-

nal should not be asserted until the following four conditions are met:

1. A bus grant has been received.

2. Address strobe is negated, which indicates that the SCM68000 is not using the bus.

3. Data transfer acknowledge is negated, which indicates that neither memory nor pe-

ripherals are using the bus.

4. Bus grant acknowledge is negated, which indicates that no other device is still claiming

to be the bus master.

2.6 INTERRUPT CONTROL (IPLB2–IPLB0)

These active-low input signals indicate the encoded priority level of the device requesting

an interrupt. Level 7, which cannot be masked, has the highest priority; level 0 indicates that

no interrupts have been requested. IPLB0 is the least significant bit of the encoded level,

and IPLB2 is the most significant bit. For each interrupt request, these signals must maintain

the interrupt request level until the SCM68000 acknowledges the interrupt to guarantee that

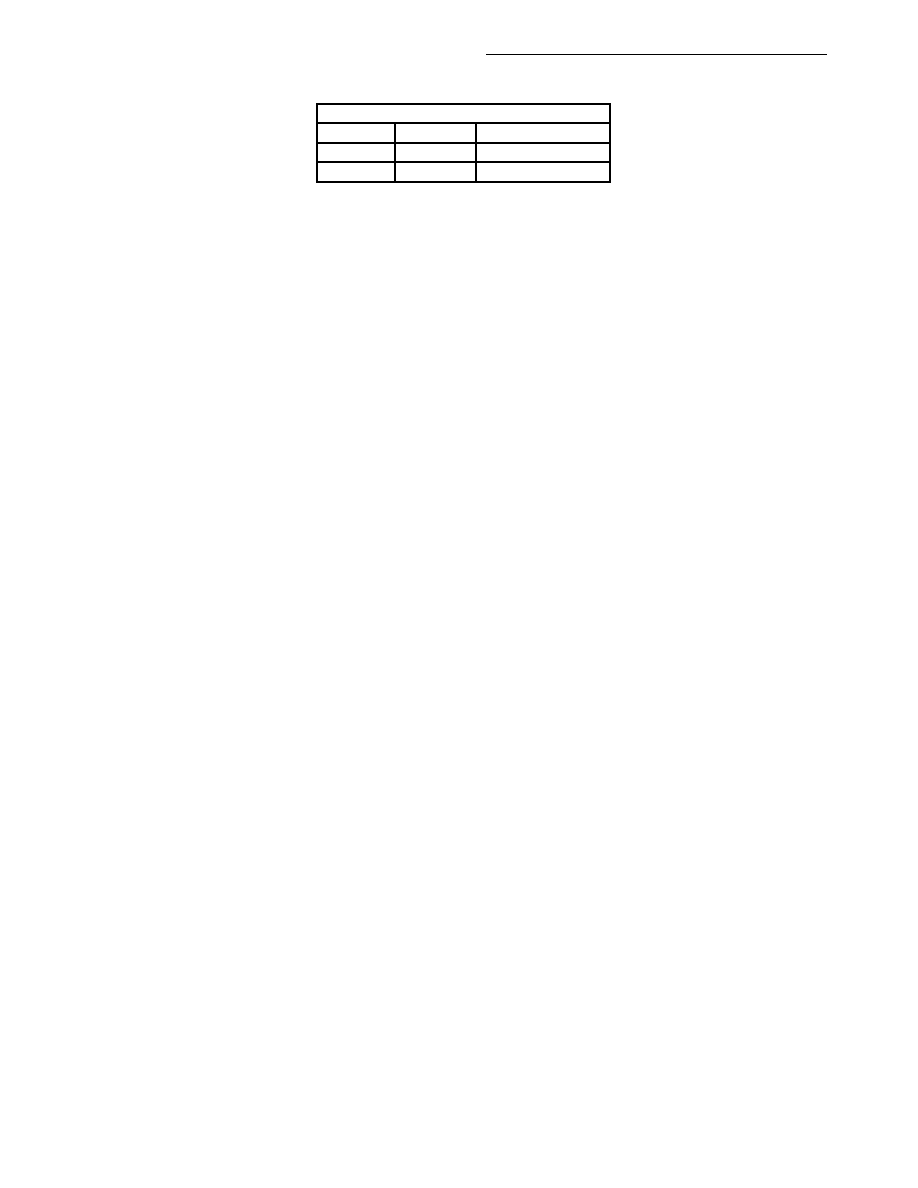

Table 2-4. Data Transfer Size

Size Code Output

SIZ1

SIZ0

Size

1

0

Byte

0

1

Word

F

re

e

sc

a

le

S

e

m

ic

o

n

d

u

c

to

r,

I

Freescale Semiconductor, Inc.

For More Information On This Product,

Go to: www.freescale.com

n

c

..

.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| EC103B | Sensitive SCRs |

| EC103B1 | Sensitive SCRs |

| EC103B2 | Sensitive SCRs |

| EC103B3 | Sensitive SCRs |

| EC103D175 | Thyristor Product Catalog |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| EC0010-000 | 制造商:TE Connectivity 功能描述:EC0010-000 |

| EC001031 | 制造商:PHOENIX 制造商全稱:PHOENIX CONTACT 功能描述:Header, Nominal current: 12 A, Rated voltage (III/2): 320 V, Assembly: Soldering |

| EC001121 | 制造商:PHOENIX 制造商全稱:PHOENIX CONTACT 功能描述:Plug component, Nominal current: 12 A, Rated voltage (III/2): 320 V, Number of positions: 4, Pitch: 5mm, Connection method: Screw connection, Color: Black, Contact surface: Tin |

| EC001283 | 制造商:PHOENIX 制造商全稱:PHOENIX CONTACT 功能描述:Plug component, Nominal current: 12 A, Rated voltage (III/2): 320 V, Number of positions: 7, Pitch: 5.08 mm, Connection method: Solder/Slip-on connection, Color: green, Contact surface: Tin, Assembly: Direct mounting |

| EC0013-000 | 制造商:TE Connectivity 功能描述:EC0013-000 |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。